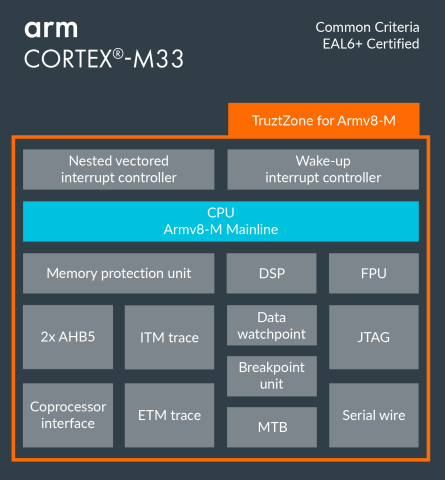

Cortex-M33

The Cortex-M33 implements the ARMv8-M architecture with a three stage in-order pipeline supporting Thumb-1 and Thumb-2, single precision Floating Point Unit, Digital Signal Processing (DSP), saturated and Custom Instructions for external co-processor accelerators.

The Nested Vector Interrupt Controller (NVIC) supports up to 480 interrupt inputs from peripherals with between 8 and 256 levels of priority.

TrustZone support for a Secure and a Non-secure state

The Memory Protection Unit supports the PMSAv8 Protected Memory System Architecture model with up to 16 regions.

The bus mechanism provides AMBA5 Code AHB (C-AHB) and System AHB (S-AHB) interfaces, and External PPB (EPPB) APB and Debug AHB (D-AHB) interfaces.

Explore This Technology

Add new comment

To post a comment on this article, please log in to your account. New users can create an account.