Use the Tabs below to find information on community projects. Project pages have links to the 'technology' and 'design flow' stages used and ways you can comment on or join a project.

- Projects are key to community hardware design

-

As a community hardware design activity we form our collaborations around shared design actions making Projects a core of the SoC Labs community. Projects help us share and reuse hardware and software developments around core Arm IP to help us in our research goals.

- A project, takes technology and uses a design flow to make a SoC.

-

A project has a timeframe and uses the two other significant aspects of a SoC development, the selection of technology or IP blocks that make up the SoC and the design flow that is followed from specification through to final instantiation of a system. Any System On Chip usually involves the use of pre-existing IP blocks. A project team can select IP from the technology section of the site during the first stage of a design flow, Architectural Design. Later stages in the design flow support the creation of the novel aspects of the SoC design.

- Projects have a type, either active, complete (case study) or being formulated (request for collaboration)

-

Sharing information on projects much earlier than traditional academic collaboration is encouraged. Historically knowledge sharing has been at the end of the research activity, with published papers and results. As well as write up of finished projects ("case study"), ongoing projects under development ("projects") there are projects that are still being formulated ("request for collaboration") listed. We want to encourage people to engage with the project teams, for example, adding a comment to a specific project page or joining a project.

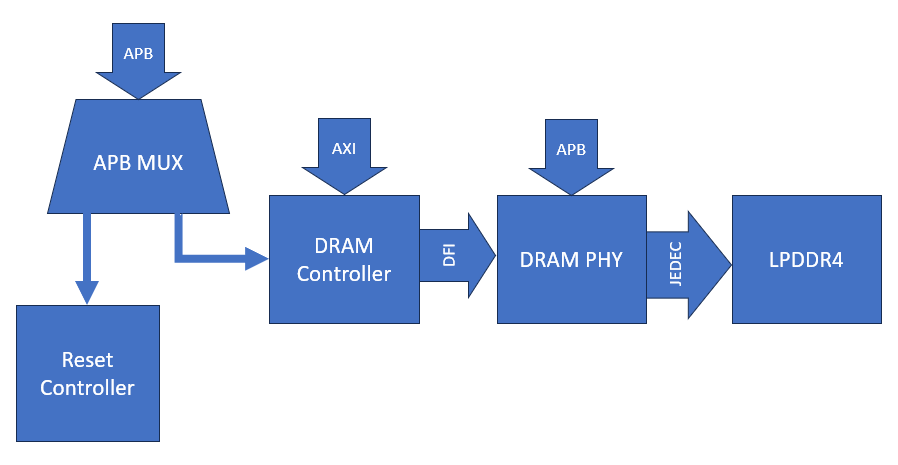

Latest Reference Design Projects

To enable full operating system support in megaSoC, a substantial amount of memory is required to accommodate the complexity of modern Linux-based software stacks, including the kernel, drivers, middleware, and user-space applications. Linux environments, unlike lightweight bare-metal systems such as nanoSoC, demand not only larger memory footprints but also consistent access to high-bandwidth memory to maintain performance across multitasking workloads. The most common approach is to incorporate external DRAM, which offers the necessary capacity and throughput.

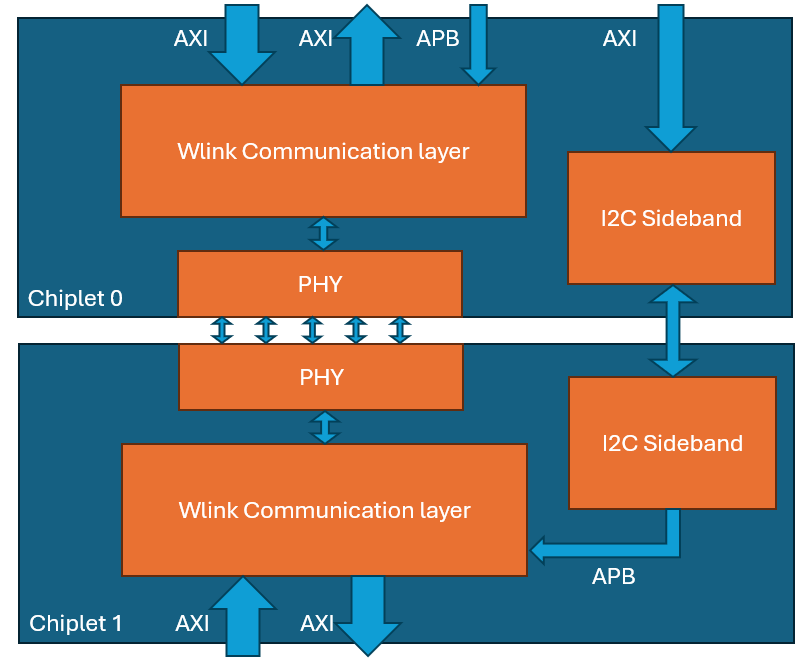

For a chiplet system, you need a communication interface between chiplets. The industry has developed standards that require complicated IPs around UCIe and the CHI interface from Arm. For many academic projects these are probably more complicated than needed . The aim of this project is to produce a simple chiplet communications interface based around the open standard AXI protocol.

The project is hosted here: https://git.soton.ac.uk/soclabs/chiplets/axi-chiplet-controller

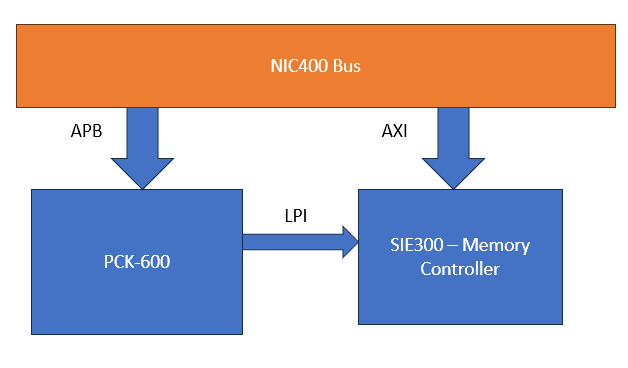

The PCK600 Arm IP provides components to allow a power control infrastructure to be distributed in a SoC in order to make a design energy efficient. Arm provide the IP as part of their Power Control System Architecture that can be used to control the power states of various parts of the system. This control of the power infrastructure is achieved through the use of the Power Policy Unit (PPU). This unit has an APB interface to allow for software control, and some low power interfaces that can connect to the power controllable IP within the system.

Latest Collaborative Projects

Precision timekeeping is a foundational service in any distributed system. Whether synchronising Ethernet frames to a PTP grandmaster, timestamping die-to-die packet exchanges between chiplets, or scheduling time-critical hardware events, the system needs a clock that is accurate, capturable at multiple points simultaneously, and adjustable by both hardware servo loops and software without stopping.

Latest Competition Projects

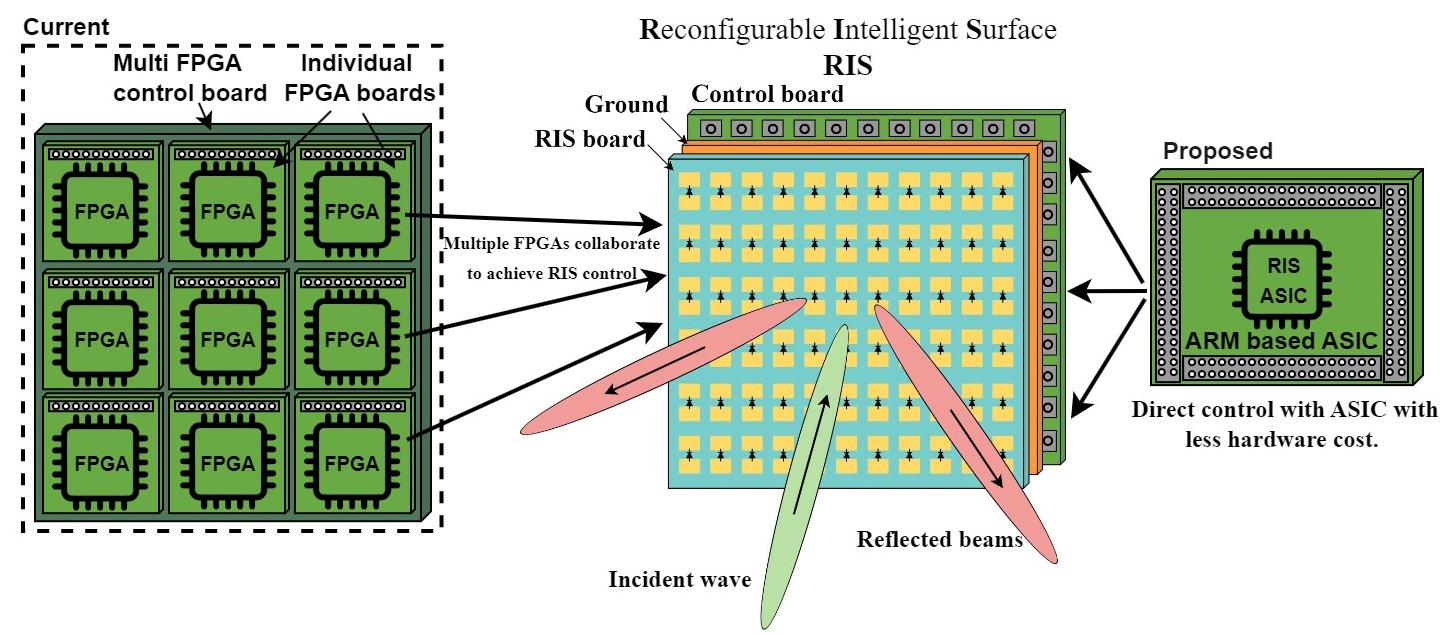

Reconfigurable Intelligent Surfaces (RIS) are planar structures composed of large arrays of tunable elements that can dynamically redirect, reflect, or shape wireless signals in the environment.

This project aims to develop an advanced RF energy harvesting (EH) receiver chip specifically designed to power embedded sensors for monitoring the condition of groceries during transportation. The receiver chip captures wireless energy transmitted from phased array antennas and converts it into electrical power that is used to operate onboard sensors, which continuously monitor critical parameters such as temperature and humidity inside delivery trucks.

Stroke and epilepsy are among the most common debilitating neurological conditions, with a worldwide prevalence of 100 million people (World Stroke Organization, 2022) and 50 million people (World Health Organization, 2024), respectively. Present-day approaches for treating neurological and neurosurgical conditions include physiotherapy, pharmacological treatment, surgical excision, and interventions such as deep brain stimulation.

In the context of Industry 4.0, handwritten digit recognition plays a vital role in numerous applications such as smart banking systems and postal code detection. One of the most effective approaches to tackle this problem is through the use of machine learning and neural network models, which have demonstrated impressive accuracy and adaptability in visual pattern recognition tasks.

Latest Completed Project Milestones

| Project | Name | Target Date | Completed Date | Description |

|---|---|---|---|---|

| DRAM Controller integration in megaSoC | Specifying a SoC | |||

| DRAM Controller integration in megaSoC | Verification Methodology | |||

| DRAM Controller integration in megaSoC | Architectural Design | |||

| DRAM Controller integration in megaSoC | Getting Started | |||

| DRAM Controller integration in megaSoC | Generate RTL | |||

| DRAM Controller integration in megaSoC | IP Selection | |||

| An Efficient Hardware-based Spike Train Repetition for Energy-constrained Spiking Neural Networks | IP Selection |

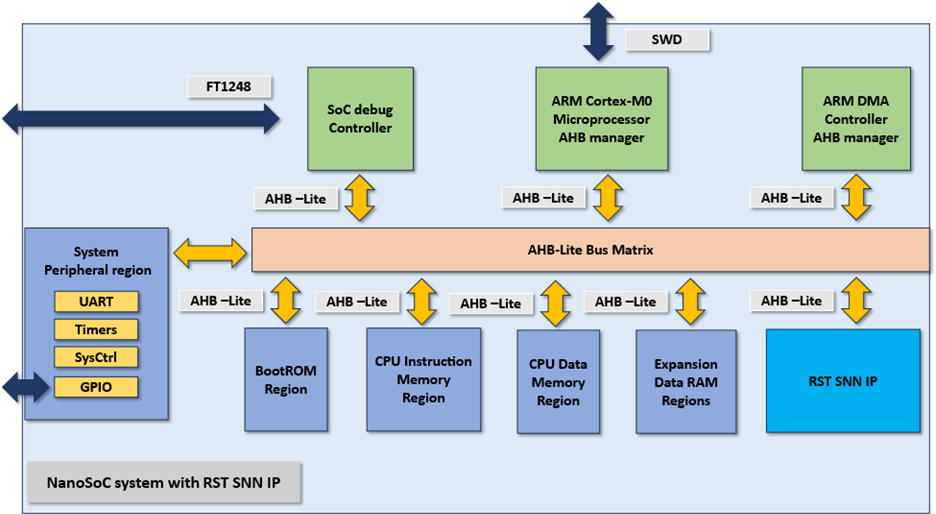

In this milestone, the IPs required to build the nanoSoC platform are identified. These IPs provide the computational core, memory hierarchy, communication interfaces, and system peripherals needed to support the integration and operation of the RST SNN IP. The SoC will include the following IPs:

System Peripherals:

This set of IPs is selected to ensure compatibility, scalability, and low power operation while meeting the functional requirements of handwritten digit recognition using SNNs |

||

| An Efficient Hardware-based Spike Train Repetition for Energy-constrained Spiking Neural Networks | Getting Started |

Project management This project will follow a standard SoC development workflow, serving as a foundational element for the NanoSoC reference platform. Although it may not proceed to full tape-out or silicon validation, the project will have milestones to ensure steady progress. Each milestone will be tracked with corresponding completion dates and documentation. To maintain agility and responsiveness, flexible intermediate goals will be established. These will help break down the overall objective—designing an energy-efficient RST-based SNN IP for handwritten digit recognition—into manageable phases, from algorithm modeling to RTL implementation and system integration. Design methods The project will adopt a top-down design methodology:

Access to IP Access to standard IP blocks (Cortex M0+ core, AHB interfaces, memory, DMA) will be provided through the nanoSoC platform, while the RST SNN IP will be developed in-house. Git to nanoSoC repository: SoCLabs / NanoSoC Tech · GitLab Git to RST SNN IP repository: |

||

| An Efficient Hardware-based Spike Train Repetition for Energy-constrained Spiking Neural Networks | Specifying a SoC |

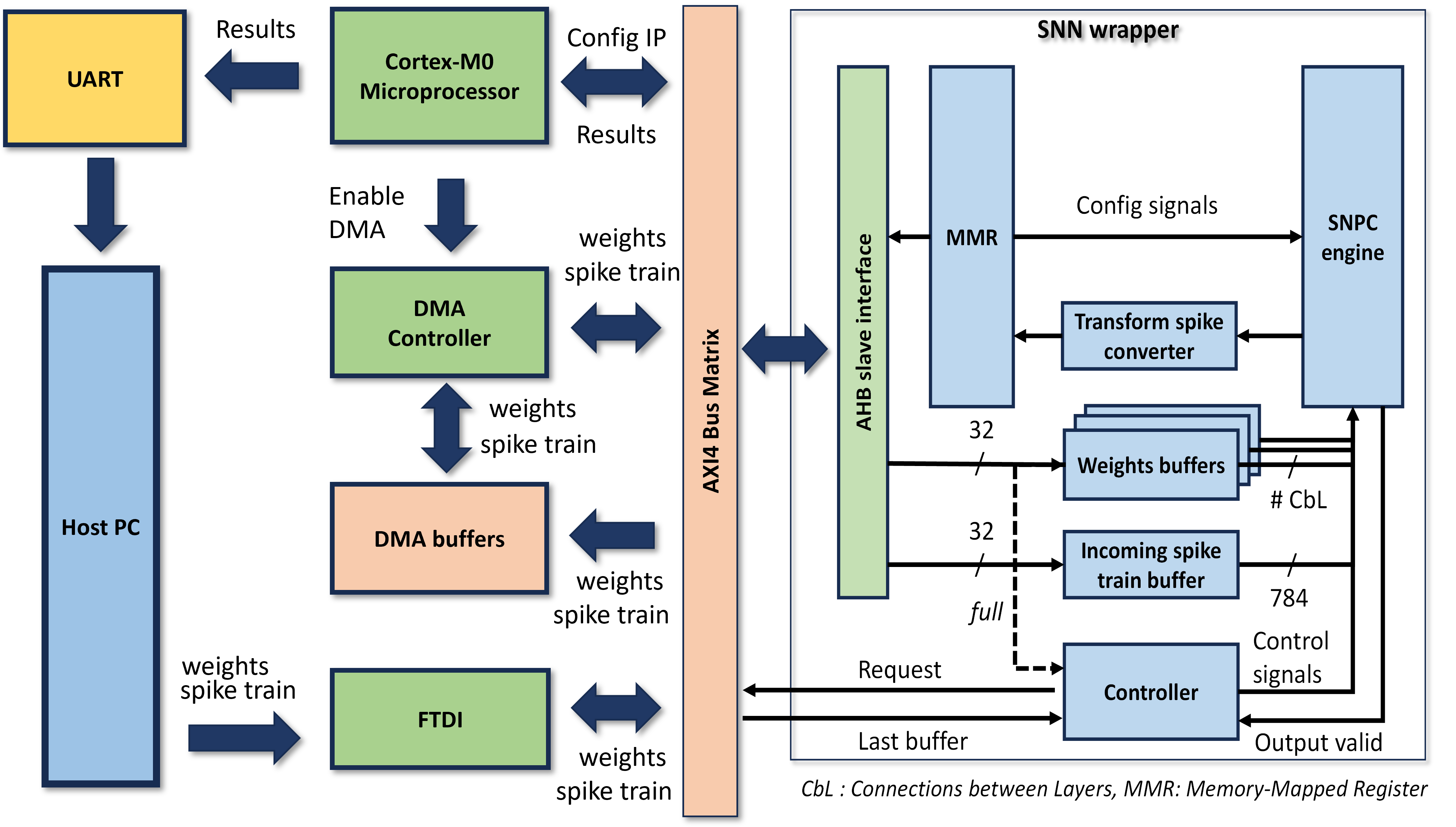

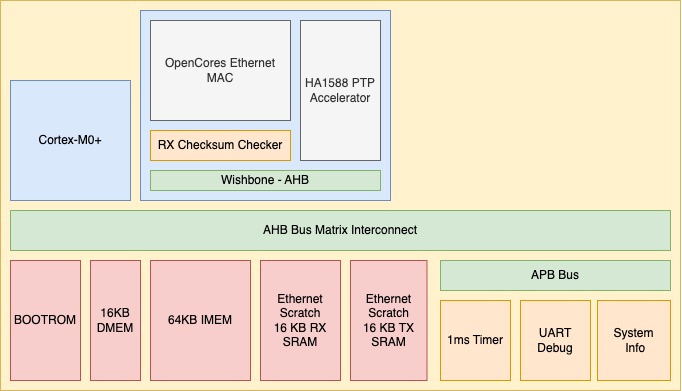

Figure 1. The overview of the architecture for nanoSoC with SNN IP This milestone focuses on defining the overall architecture of the NanoSoC system, integrating both general-purpose components and the custom RST SNN IP accelerator. The SoC architecture is centered around a lightweight Arm Cortex-M0 processor, with system-level connectivity managed via the AMBA AHB-Lite bus. Key components and architectural decisions include:

This modular SoC architecture is designed with flexibility and scalability in mind, enabling easy expansion or substitution of components. It also ensures low-power operation suitable for edge AI applications focused on handwritten digit recognition.

Figure 2. The details of our proposal architecture |

||

| An Efficient Hardware-based Spike Train Repetition for Energy-constrained Spiking Neural Networks | data model |

In this milestone, the dataset and initial SNN architecture for handwritten digit recognition are defined. The MNIST dataset is selected due to its wide use as a benchmark for image classification tasks and its suitability for validating lightweight neural architectures on resource-constrained platforms. The chosen SNN model consists of four layers:

The structure is designed to balance classification performance and hardware efficiency, laying the groundwork for implementing the RST optimization in future milestones. |

Daniel Newbrook

Daniel Newbrook

David Mapstone

David Mapstone

Zhicheng Shen

Zhicheng Shen

Fidel Makatia

Fidel Makatia

The Anh Nguyen

The Anh Nguyen