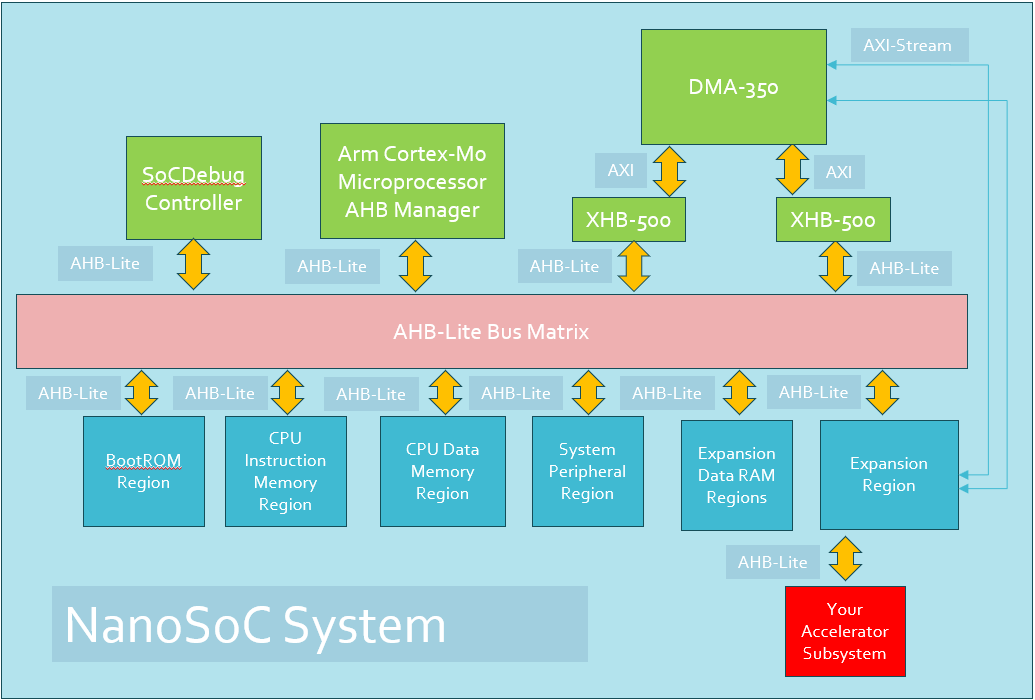

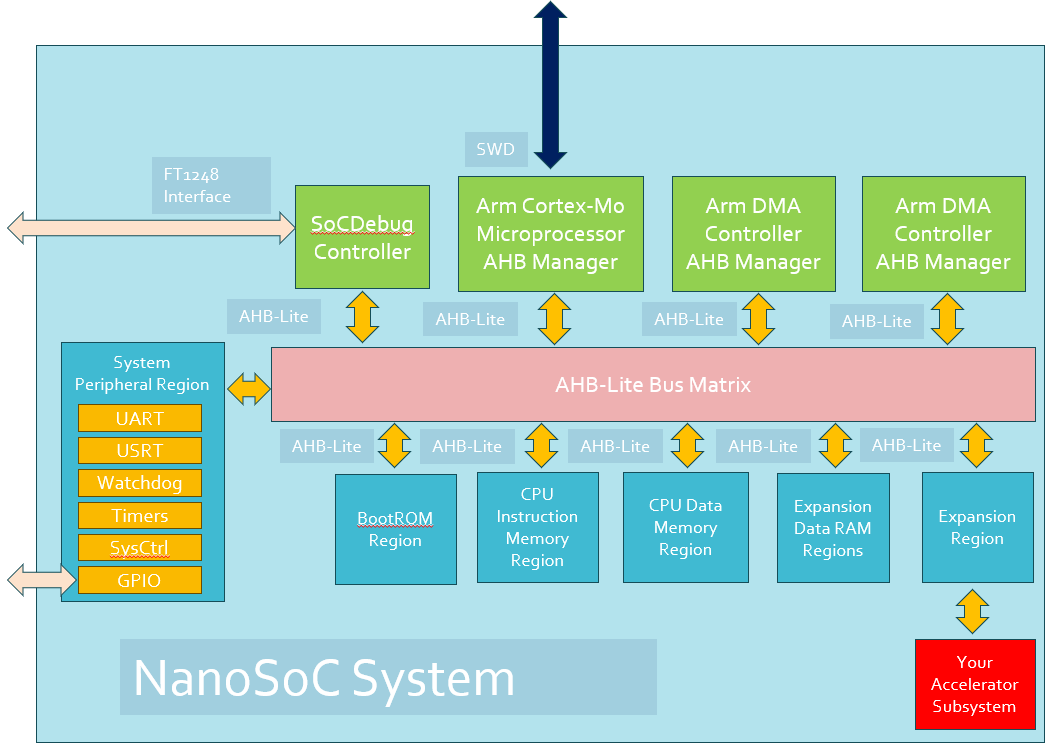

A physical test environment is required for ASIC devices fabricated following tape out. The nanoSoC test board provides a complete test environment for ASIC designs based on the nanoSoC reference design and enables the showcase of any custom designs that utilise it. Reviewing the function of nanoSoC identifies a number of design criteria for the test board:

Daniel Newbrook

Daniel Newbrook

David Flynn

David Flynn