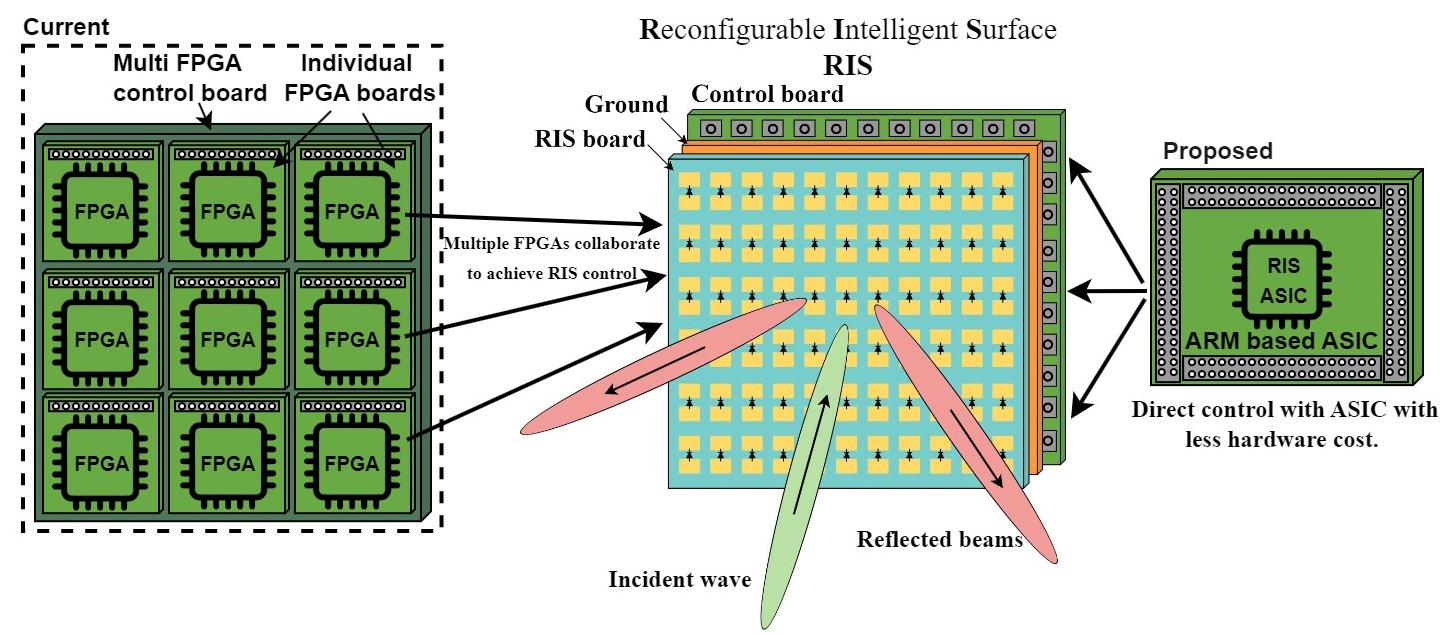

Reconfigurable Intelligent Surfaces (RIS) are planar structures composed of large arrays of tunable elements that can dynamically redirect, reflect, or shape wireless signals in the environment.

Reconfigurable Intelligent Surfaces (RIS) are planar structures composed of large arrays of tunable elements that can dynamically redirect, reflect, or shape wireless signals in the environment.

This project aims to develop an advanced RF energy harvesting (EH) receiver chip specifically designed to power embedded sensors for monitoring the condition of groceries during transportation. The receiver chip captures wireless energy transmitted from phased array antennas and converts it into electrical power that is used to operate onboard sensors, which continuously monitor critical parameters such as temperature and humidity inside delivery trucks.

Stroke and epilepsy are among the most common debilitating neurological conditions, with a worldwide prevalence of 100 million people (World Stroke Organization, 2022) and 50 million people (World Health Organization, 2024), respectively. Present-day approaches for treating neurological and neurosurgical conditions include physiotherapy, pharmacological treatment, surgical excision, and interventions such as deep brain stimulation.

In the context of Industry 4.0, handwritten digit recognition plays a vital role in numerous applications such as smart banking systems and postal code detection. One of the most effective approaches to tackle this problem is through the use of machine learning and neural network models, which have demonstrated impressive accuracy and adaptability in visual pattern recognition tasks.

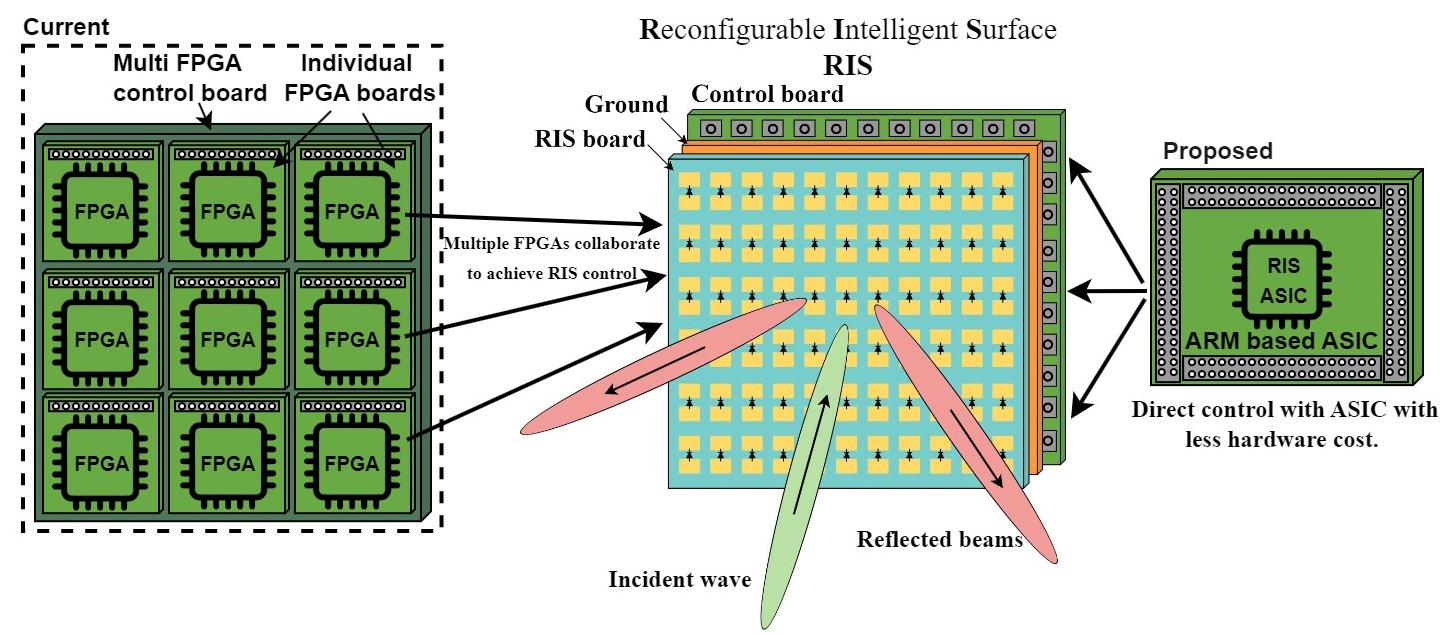

Aspen is a unified accelerator for deep neural network (DNN)-based extended reality perception workloads. Aspen proposes a mixed-precision quantization scheme using the posit datatype to reduce memory usage while maintaining accuracy, a DNN accelerator for mixed-precision posit datatypes, and efficient data prefetching and data layout to minimize data reorganization. The Aspen system-on-chip has an Arm Cortex-M3 CPU, a mixed-precision posit-based DNN accelerator, and 4 megabytes of SRAM partitioned into eight 512 KB banks, connected through a 128-bit-wide interconnect.

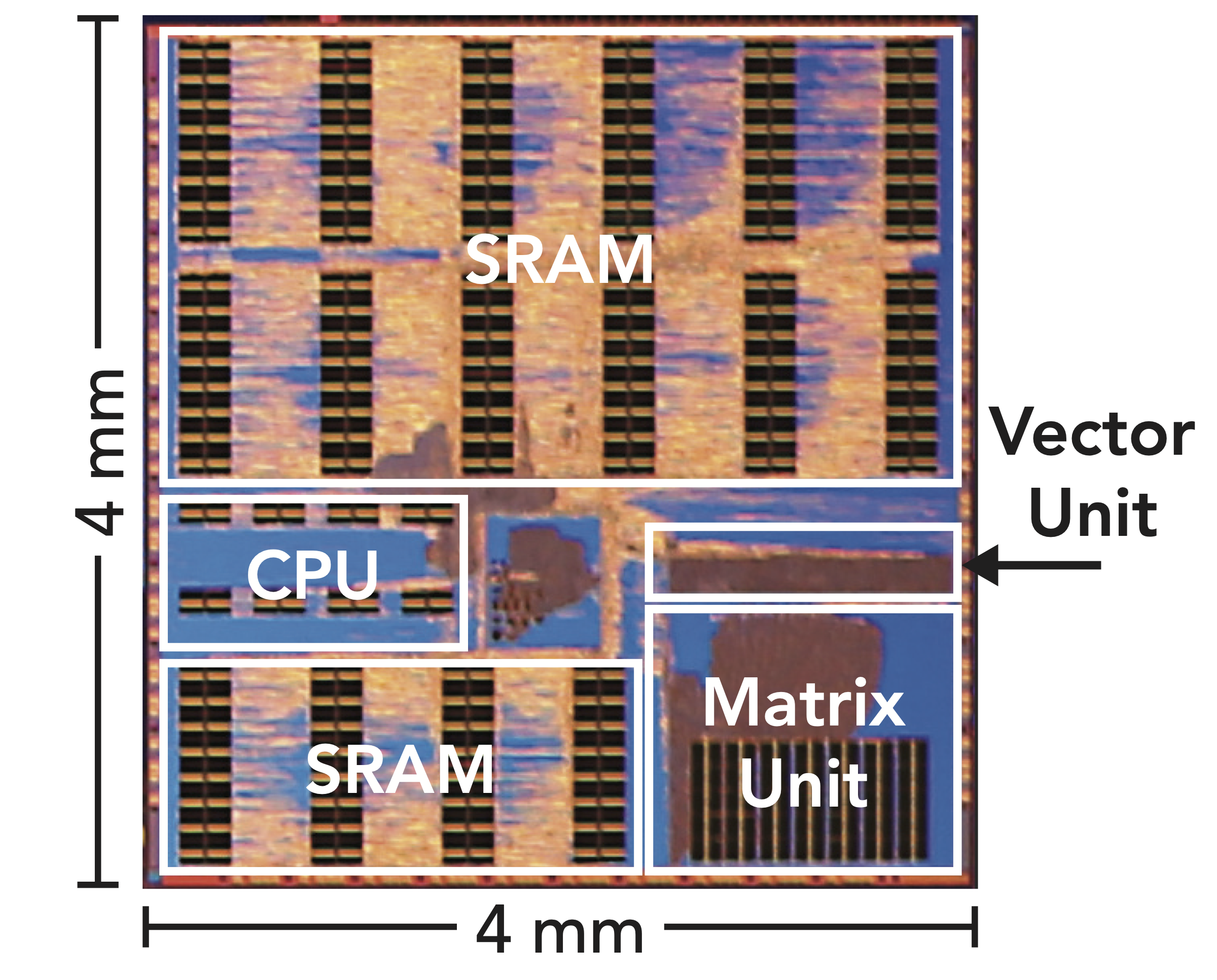

Our innovative SoC design for precision agriculture revolutionizes field management by deploying a robust mesh network of sensor-based devices, capable of detailed monitoring and swift response to variations in soil health, erosion, drought, and pest activities. This system not only ensures reliability through its mesh architecture—eliminating single points of failure—but also incorporates diverse sensors for comprehensive data acquisition. It's engineered for energy efficiency to sustain operation throughout an entire crop season, significantly optimizing resource use and reducing waste.

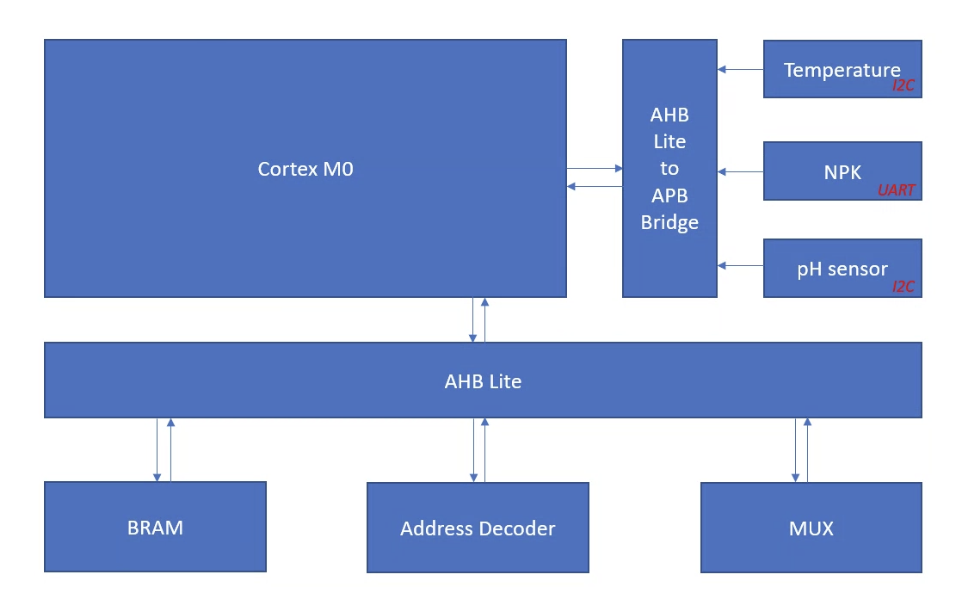

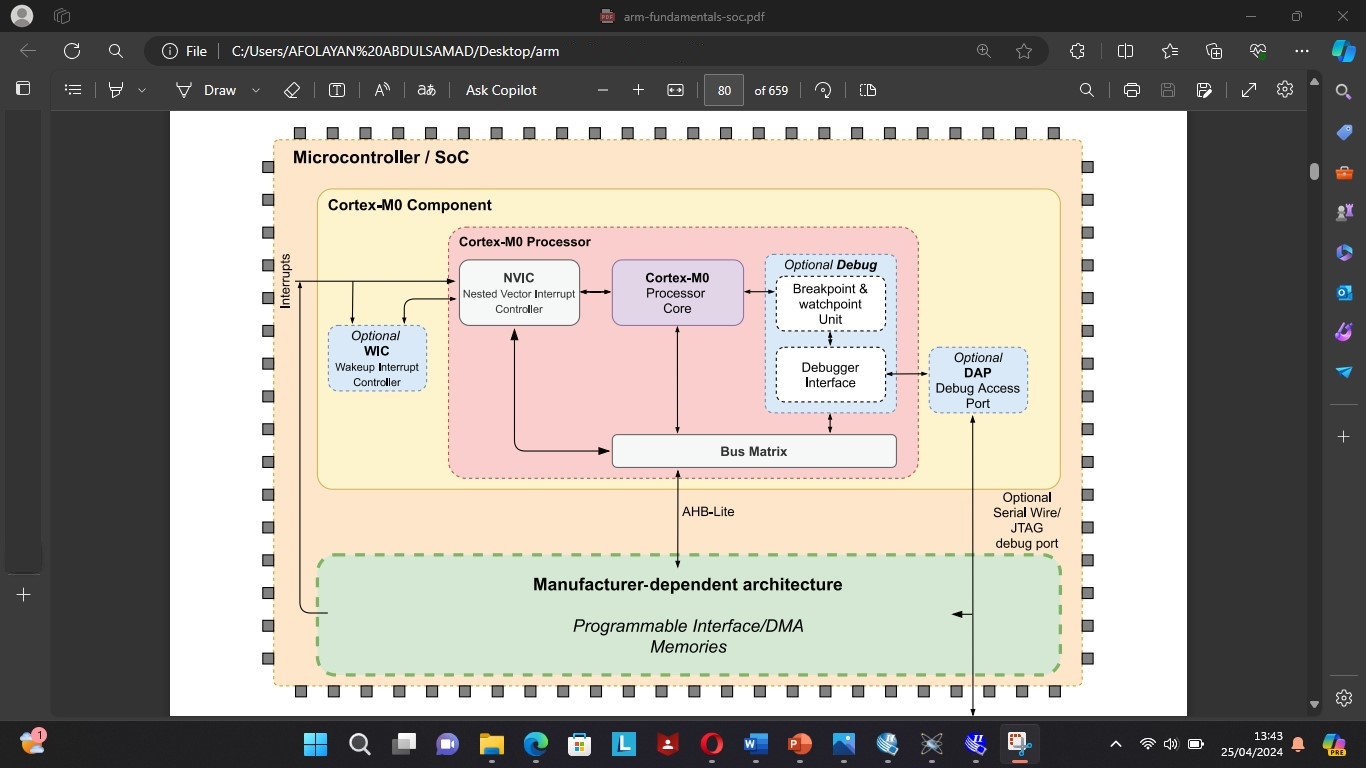

This project focuses on developing a plant growth monitoring system for space exploration missions using the ARM Cortex-M0 microcontroller core. The projects aim to develop a SOC based on ARM M0 core for interactive plant monitoring by interfacing AHB lite, GPIO, timers, and communication protocols such as UART, I2C, SPI, and co-processors. This project also proposes two co-processors for interactive plant monitoring and control. One AI co-processor for classification and prediction of plant and environmental data.

Nowadays, rotating machine is the power source for most production equipment and is widely used in manufacturing factories. Common rotating machinery mainly includes bearings, gears, shafts, and the others. However, rotating machines suffer from frequent collisions and vibrations which lead to wearing and aging, which increases the chance of failure in the overall system operation. This make the cost of factories increase and the quality of production deteriorate. Therefore, the industries gradually value the usage of accurate and efficiency predictive maintenance system.

This Project is to develop traffic light system that can reduce traffic congestion with the aid of counters for each lane and acts wisely with the intersection in real time based with a fixed time constrain, include both hardware and software requirements using SOC FPGA technology with fundamental specification for the Register Transfer Level (RTL).