Mali-G52

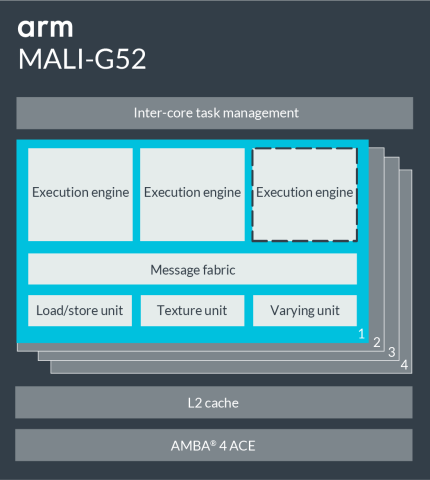

The G52 implements the Bifrost architecture supporting OpenGL 2.0 and Vulkan and Machine Learning (ML) and Augmented Reality (AR) with support for 8 bit dot product operations. It can have upto 4 shader cores operating with a 850 MHz clock, 16k load/store cache, Level 2 cache size configurable form 32kB to 512kB depending on core count. AMBA ACE-LITE and AXI bus interface. Support for Arm Frame Buffer Compression (AFBC) and Adaptive Scalable Texture Compression (ASTC).

The G52 has a 768 thread pool, each execution engine has eight arithmetic logic units (ALU) possessing separate Fused Multiply Add (FMA) and ADD/SF and 8 bit dot product pipes, two texture units responsible for all memory access to do with textures and the load/store unit is responsible for all shader memory accesses which are not related to texturing.

Explore This Technology

Add new comment

To post a comment on this article, please log in to your account. New users can create an account.