Debug & Trace

No matter how much work is done to ensure a design is correct it is likely issues will need to be discovered, identified and corrected. Ensuring an effective and efficient debug environment is important.

As a design evolves towards a physical implementation the debug and trace environment needs the be established and maintained. Arm IP blocks come with debug and trace capabilities. Depending on the specific SoC implementation custom debug capabilities may need to be added to the design. The debug environment needs to ensure all the appropriate debug and trace data is passed to the SoC designers to reduce debug time and effort. In a SoC implementation a modular approach is needed with standardized debug interfaces. The Arm CoreSight Debug & Trace IP supports a modular approach to establishing the SoC debug environment.

In debug environments two terms often mentioned are Observability and Controllability. As well as getting debug and trace data out the designer needs to control the system under test.

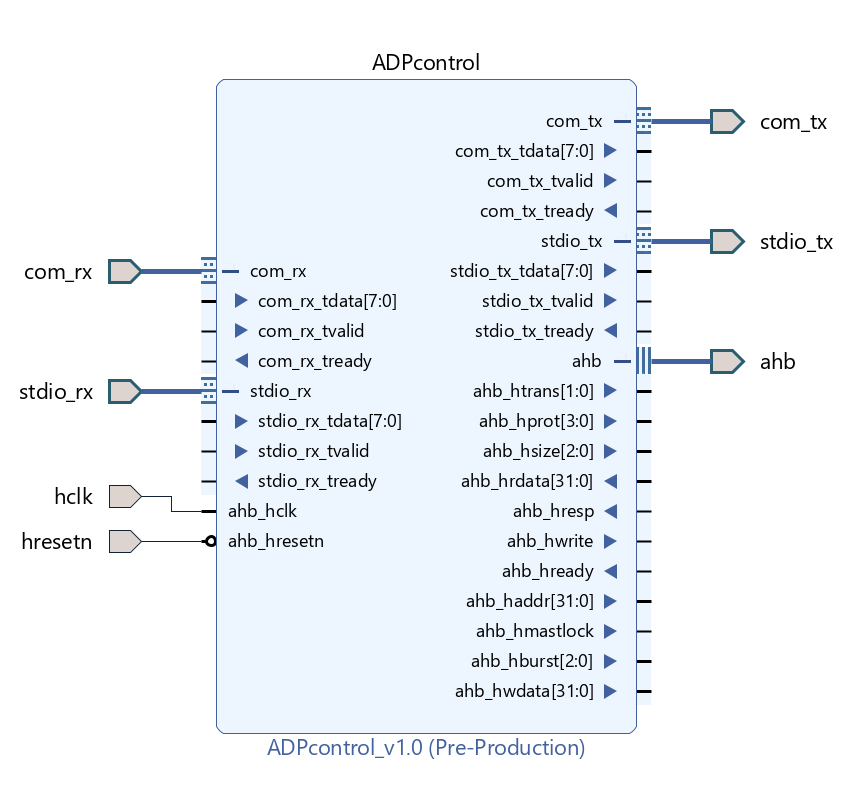

A fundamental component of CoreSight is the Debug Access Port (DAP) which provides a connection from the designer's debug enviroment to the part of the SoC under test. A SoC may have multiple DAPs. The implementations of a DAP should comply with an Arm Debug Interface (ADI) Architecture Specification ensuring easy use within the Arm Development Studio platform.

CoreSight supports physical connection interfaces via standards such as JTAG or Serial Wire Debug.

Explore This Technology

Projects Using This Technology

Add new comment

To post a comment on this article, please log in to your account. New users can create an account.