Low power design

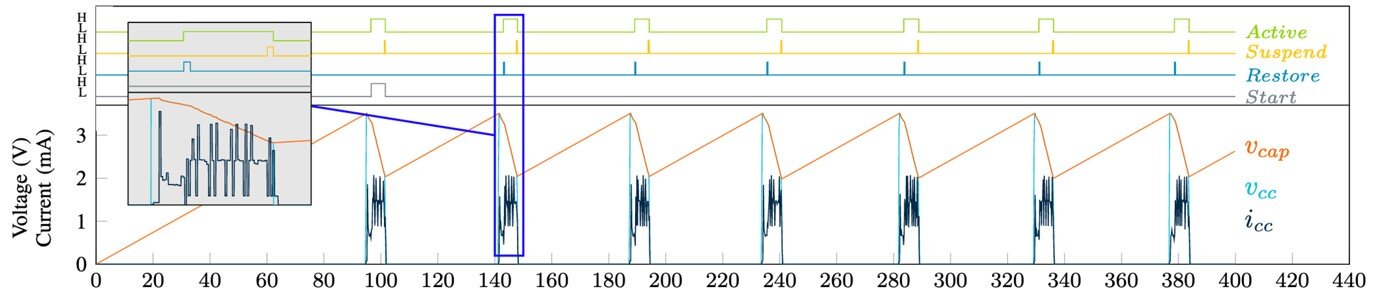

Designing components and systems with an emphasis on minimizing active (dynamic) and standby (static) power consumption. Increasingly this is addressed by careful logical design of the design in RTL together with companion "power intent", provided as Unified Power Format (UPF) annotation, standardized in IEEE 1801 specification.

Explore This Interest

Projects Using This Interest

Reference Design

Active Project

Reference Design

Active Project

Reference Design

Active Project

Competition 2024

Competition: Hardware Implementation

Competition 2023

Competition: Hardware Implementation

Known Good Die

Known Good Die

Collaborative

Active Project

Experts and Interested People

Members

Name

Research Area

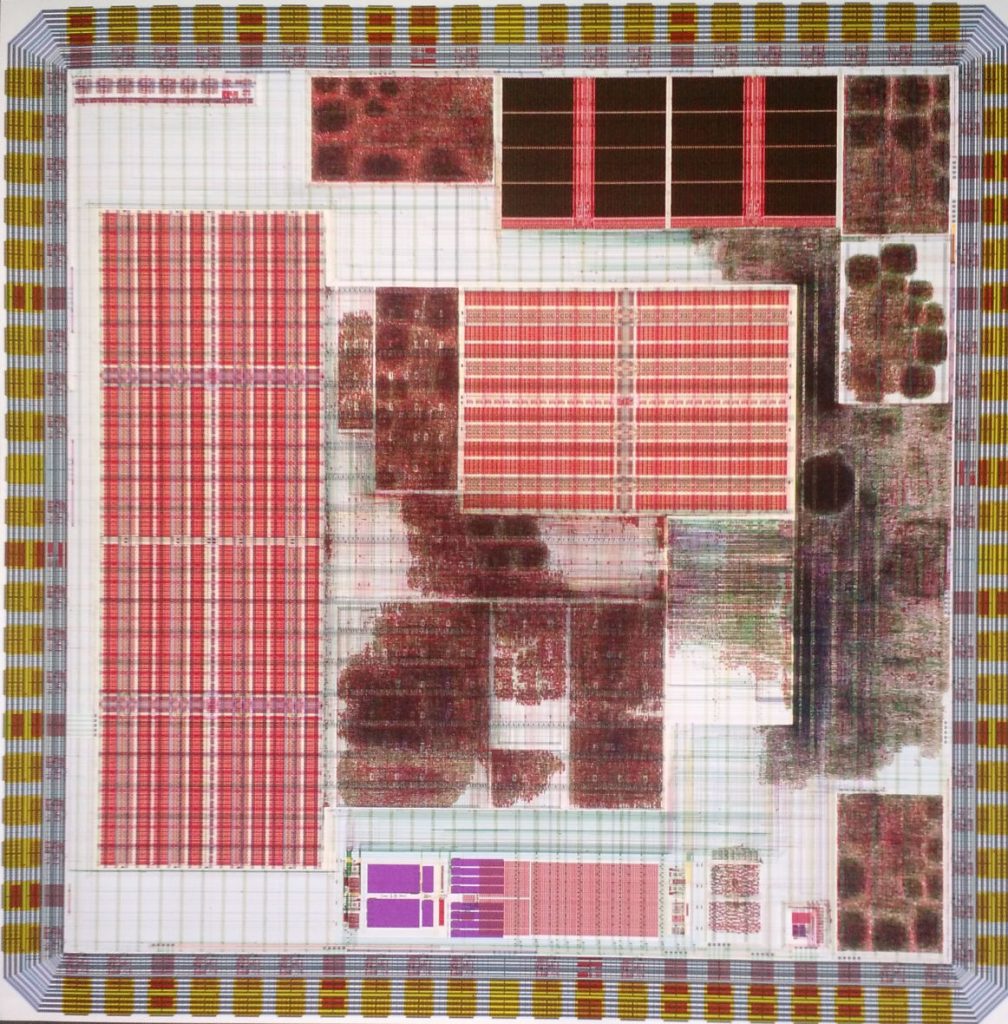

SoC integration and Verification, High Performance low power processor design

Role

Digital Design and Verification Engineer

Name

Research Area

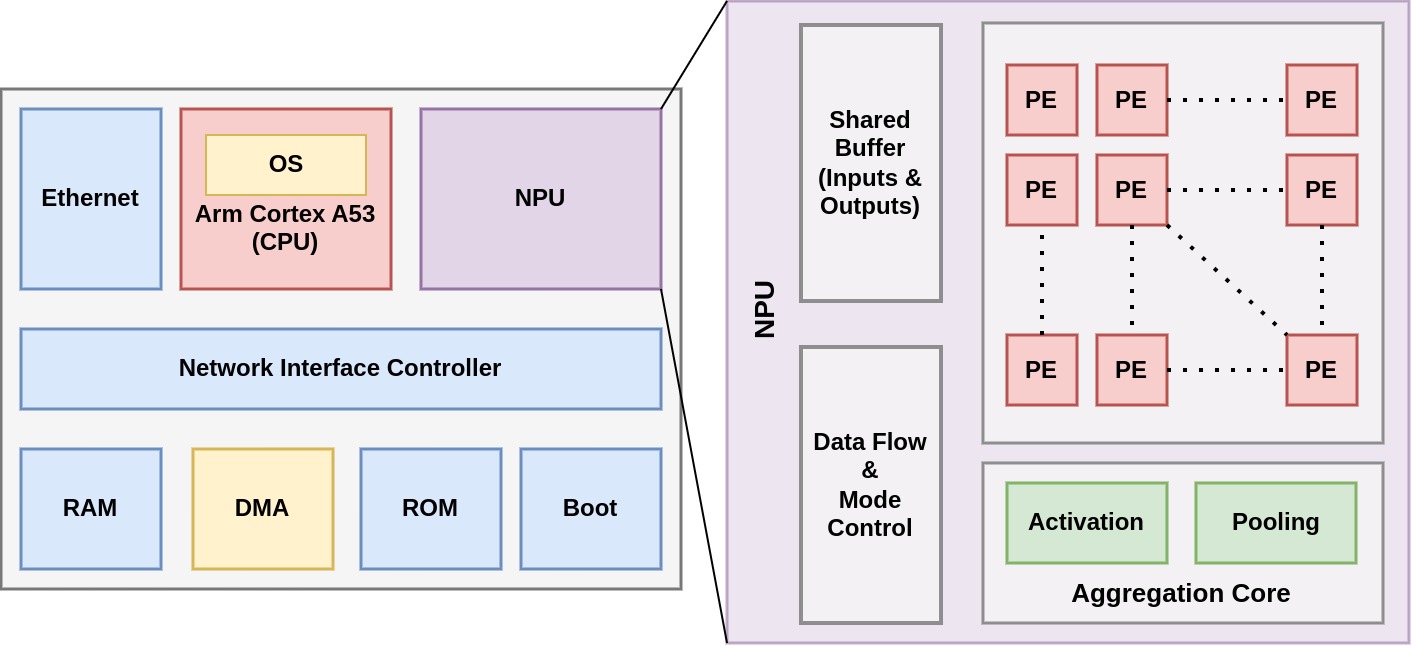

Machine Learning on Resource-Constrained Embedded Systems

Role

PhD Student

Name

Research Area

Precision Data Converters

Role

Analog/Mixed-Signal (AMS) Design Verification Engineer at Analog Devices, Inc.

Comments

Expanding this area of interest

Hi,

There are quite a few people signed up to this interest. It would be great if people could add resources or content of interest. It is easy to do. Just click on the Edit tab when logged in.

Once you are happy with your submission. Save to Editorial review.

You can also simple add a comment, or reply to this one.

We look forward to hearing from you.

Add new comment

To post a comment on this article, please log in to your account. New users can create an account.