megaSoC Prototyping using HAPS-SX

The design flow step described here enables the deployment, evaluation and Pre-silicon ASIC prototyping of large SoC designs using a Synopsys HAPS-SX, a modular, high capacity and high performance FPGA-based system. At SoC Labs, a HAPS-SX system with an AMD-Xilinx Virtex UltraScale+ VU19P FPGA, which has 8,938K logic cells, and a total of 90 Mb BRAM is being used to prototype the megaSoC design by mapping the RTL onto FPGA hardware for system-level validation.

Connecting to the HAPS system

The HAPS-SX system is managed as a virtual service by a dedicated control host (computer), which provides system management, FPGA programming, and runtime access to the HAPS-SX chassis. The HAPS-SX system typically connects to the control host via a high-bandwidth UMRBus (Universal Multi-Resource Bus) over a PCIe interface, using a provided MGB (Multi-Gigabit Board) adapter kit, or via Ethernet. The PCI Express connection is used for high-speed FPGA programming and runtime communication between the control host and the design running on HAPS-SX, while the Ethernet connection is used for design I/O, software-driven validation, or network-based communication. These connections provide access to interfaces such as JTAG and UART and support system configuration, reset control, and console output monitoring, allowing developers to interact with, and debug, the running SoC prototype.

Users do not connect directly to the HAPS-SX chassis. All user interaction occurs through the control host using remote access protocols such as Secure Shell (SSH). The control host must run a Synopsys-supported Linux distribution. Supported operating systems are listed in the HAPS Installation and Release Documentation.

Configuring the HAPS system

Comprehensive instructions for setting up the HAPS system are provided in the HAPS Installation and Release Documentation.

Synopsys provides dedicated HAPS configuration tools for system configuration. Most HAPS environments include:

- HAPS ProtoCompiler / ProtoCompiler DX - partitioning, synthesis orchestration, build flow, database, etc.

- HAPS system configuration - power, clocks, connector power, resets, programming mode, etc.

- Debug/visibility tools - often Identify / HAPS debug environment, depending on your licenses, etc.

FPGA vendor tools are used for the programming of the FPGA devices. Similarly to nanosoc, at SoC labs, Xilinx's Vivado Design Suite is used. Xilinx's Vivado software suite provides a comprehensive toolset for developing FPGA designs. It is essentially a tool that turns an RTL design into a bitstream that runs on the FPGA.

Overall Prototyping Flow

The prototyping process follows these stages:

RTL integration

Simulation-based validation

FPGA synthesis and implementation

Bitstream generation

Deployment to HAPS hardware

Hardware debug and validation

1. RTL Integration

The MegaSoC reference design is an Arm Cortex-A53 based SoC designed for research projects and targeting an ASIC tape-out. The original a53 compute system RTL within the Arm AAA IP bundle targets an ASIC flow. The work described here adapts that system RTL for pre-silicon validation on an FPGA. This supports an FPGA verification environment that can speed up the full SoC design process which may include any research specific IP.

| Task | Status | |

I | FPGA top-level wrapper | Complete |

II | ASIC SRAM macro replacement models | Complete |

III | Clock gate cell stub | Complete |

IV | XDC pin constraints | Complete |

V | UART0 routing | Complete |

VI | DRAM AXI error slave | Complete |

VII | DDR4 controller integration | Ongoing |

I. The megaSoC RTL is integrated into a top-level wrapper (haps_top), which adapts the SoC design to the FPGA environment.

The key contributions of this wrapper are:

- clock input handling

- reset synchronisation and delayed release

- generation of an internal real-time clock

- heartbeat signal generation

- UART signal routing

- QSPI interface breakout

II. The Arm Cortex-A53 RTL instantiates foundry SRAM macros that are not available in the FPGA flow. A simulation shim library provides behavioural replacements. In more detail, the Arm-delivered wrapper RTL is left unmodified, while a separate simulation model file provides FPGA-compatible definitions.

III. On ASICs, clock gating is safe as the clock trees are optimised as part of the physical designed to support it. The tools and libraries used in the later physical design stages are able to understand and manage such clock gating. FPGAs use special logic to implement clock networks, and gating them degrades the clock signals (skew, glitches, etc.). To solve this, a stub file models a gated clock so the design can be elaborated and simulate correctly.

IV. To define the input clock to the system under test, an XDC constraints file is created which maps the top-level ports to the HAPS-SX VU19P package pins. The pin assignments are listed below:

| Signal | Package Pin | Function |

| HAPS_CLK_IN | BM44 | System clock (20 MHz) |

| HAPS_RESET_N | BK44 | Active-low reset |

| HB | BF14 | Heartbeat LED |

| QSPI_SCLK | CA49 | Flash serial clock |

| QSPI_nCS | CB49 | Flash chip select |

| QSPI_IO[0] | CC49 | Flash data 0 |

| QSPI_IO[1] | CC50 | Flash data 1 |

| QSPI_IO[2] | CA51 | Flash data 2 |

| QSPI_IO[3] | CB51 | Flash data 3 |

FPGA block design for SoC test-bench

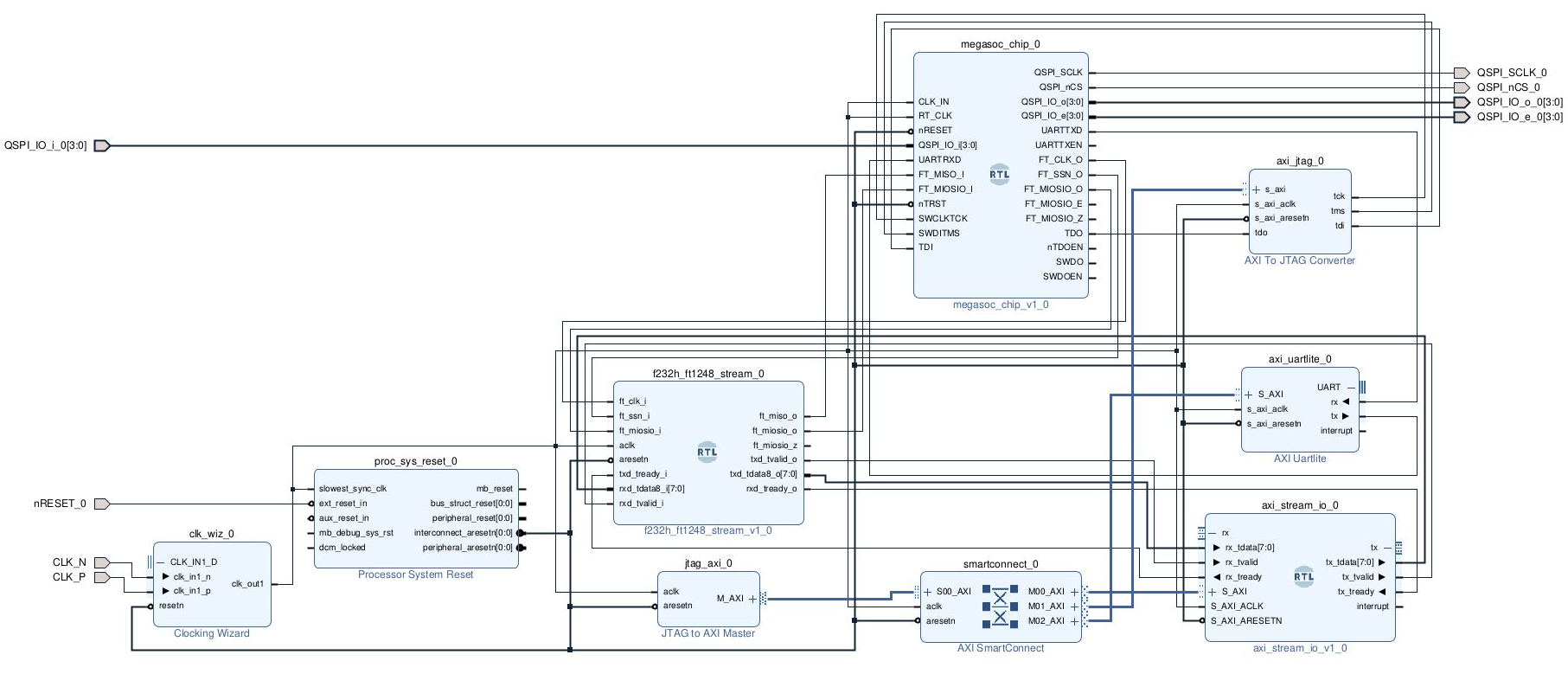

An FPGA block design defines how the SoC RTL and supporting infrastructure are integrated within the HAPS-SX environment.

The above image shows the block diagram for the FPGA debug environment. This includes a JTAG to AXI component, which uses the Xilinx Virtual Cable to interface with the JTAG side. tcl commands are used to write to that AXI interface (as seen here). This AXI interface then drives: a UART component, a JTAG component, and an FT1248 component. The UART is connected to the UART peripheral within MegaSoC, and the JTAG is connected to the DAP-lite that is used to debug the Cortex A53. The FT1248 component connects to the ADP controller in megaSoC.

The ADP controller was originally created as an easy to use debugger for the nanoSoC. It takes an ASCII character as input and generates AHB-lite commands to the SoC. The addition of the ADP controller in megaSoC may only be temporary as we assess its suitability for this full AXI system. But this does, however, enable the reuse of SoC Labs resources and a known use case for debugging in an FPGA.

By instantiating these interfaces alongside the SoC logic, the prototype supports real-time validation of the megaSoC behaviour and provides mechanisms to use standard debug tools.

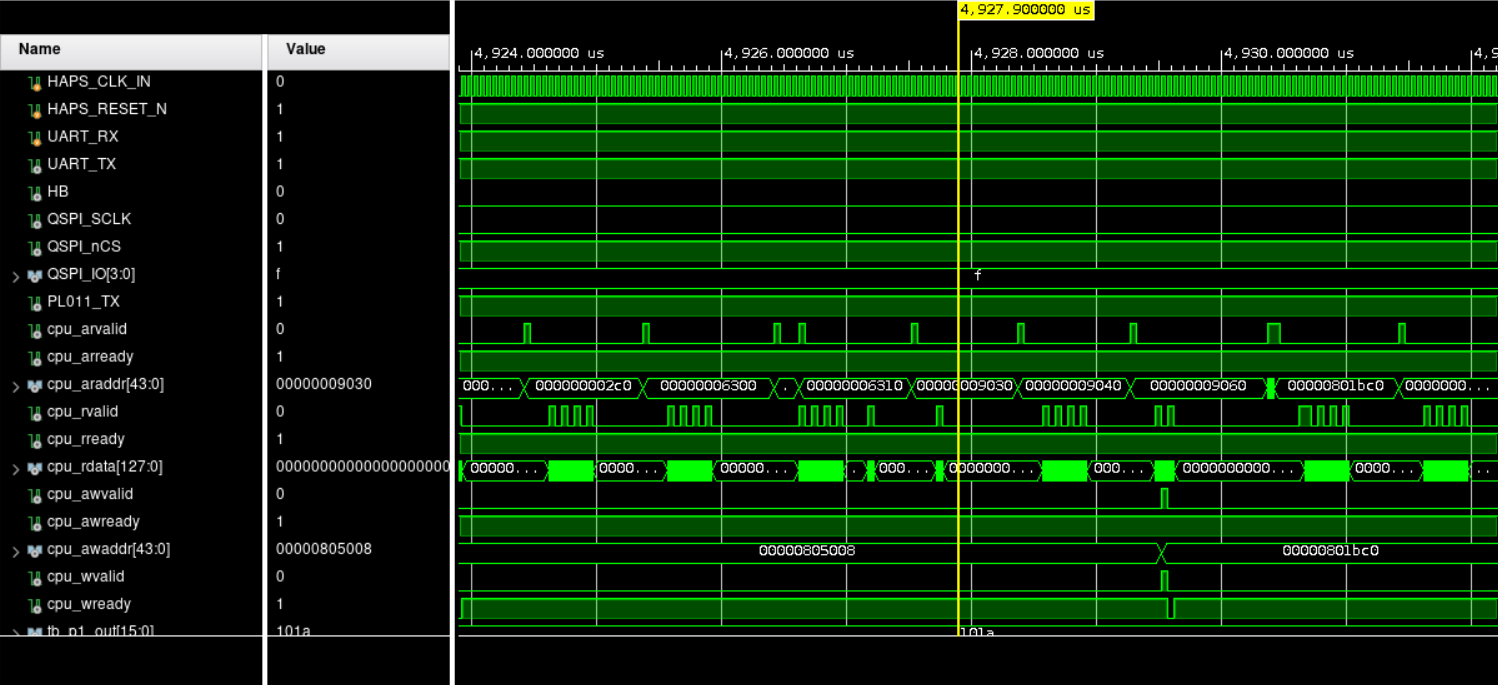

2. Simulation-Based Validation

Before FPGA synthesis, the system is validated in simulation. The checks performed are:

- reset release

- internal counter activity

- heartbeat toggling

- CPU AXI transactions (fetch/read/write)

- peripheral bus activity

- UART output observation

FPGA build scripts

To Be Added

FPGA Programming

To Be Added

SoC emulation and programming

To Be Added

Add new comment

To post a comment on this article, please log in to your account. New users can create an account.