View Collaborative Projects

Precision timekeeping is a foundational service in any distributed system. Whether synchronising Ethernet frames to a PTP grandmaster, timestamping die-to-die packet exchanges between chiplets, or scheduling time-critical hardware events, the system needs a clock that is accurate, capturable at multiple points simultaneously, and adjustable by both hardware servo loops and software without stopping.

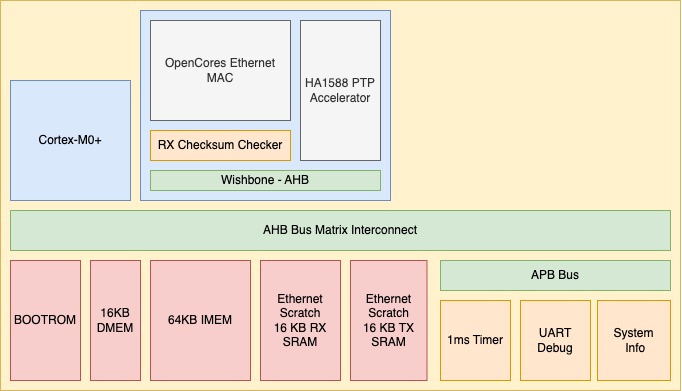

This program is dedicated to the development of a System on Chip (SoC) platform, specifically designed to support learning and research activities within Indonesian academic institutions. The platform serves as an educational and research tool for students, lecturers, and researchers to gain hands-on experience in digital chip design.

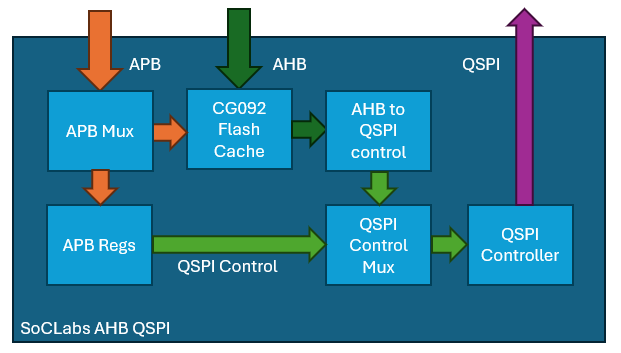

The instruction memory in the first tape out of nanosoc was implemented using SRAM. The benefit was the read bandwidth from this memory was very fast, the downside was on a power-on-reset, all the code was erased as SRAM is volatile memory. An alternative use of non-volatile memory would benefit applications where deployment of the ASIC does not allow, or simply time is not available for programming the SRAM after every power up.

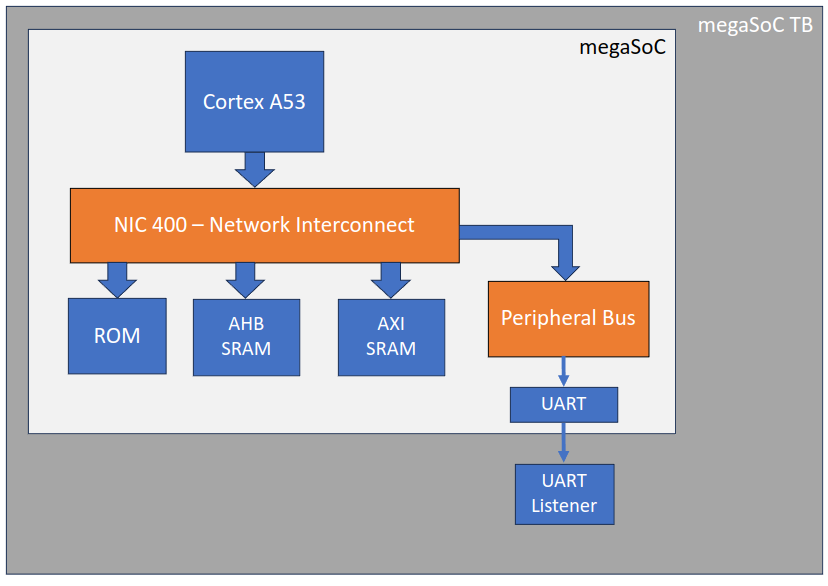

There is growing interest within the SoC Labs community for an Arm A-Class SoC that can support a full operating system, undertake more complex compute tasks and enable more complicated software directed research. The Cortex-A53 is Arm's most widely deployed 64-bit Armv8-A processor and can provide these capabilities with power efficiency.

This project aims to design and implement a high capacity memory subsystem for Arm A series processor based SoC designs. The current focus of the project is the design and implementation of a Memory Controller for DDR4 memory.

The Synopsys HAPS® System adds additional capabilities to the FPGA-based prototyping environments SoC Labs can use to support projects. The HAPS® system provides a greater amount of logic resources supporting the development of larger SoC designs. It can be used to support multiple projects simultaneously. It is used by many semiconductor companies, including ARM, for their CPU verification. This collaboration project will use the HAPS® system in SoC Labs projects and share with the community experience in utilising such systems.

David Mapstone

David Mapstone

Trio Adiono

Trio Adiono

Daniel Newbrook

Daniel Newbrook

Srimanth Tenneti

Srimanth Tenneti

John Darlington

John Darlington