Hardware design

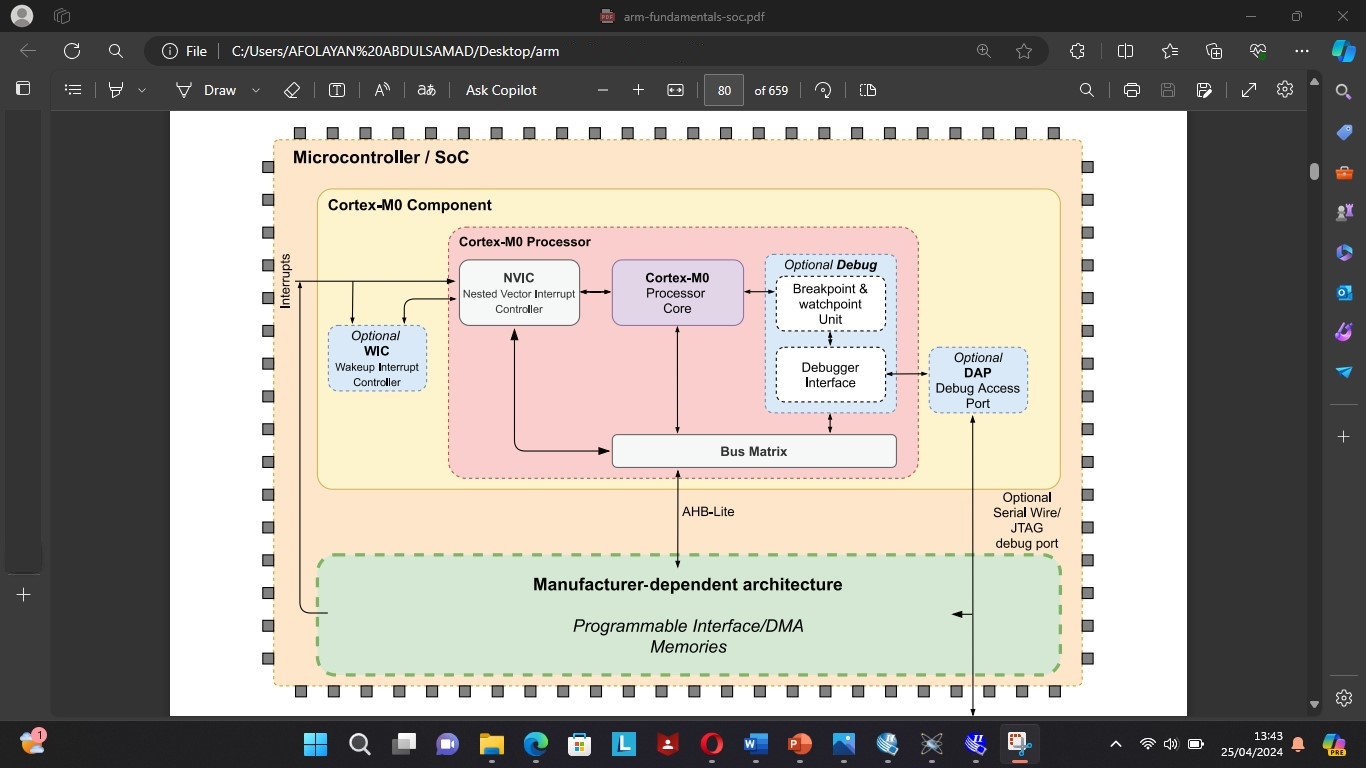

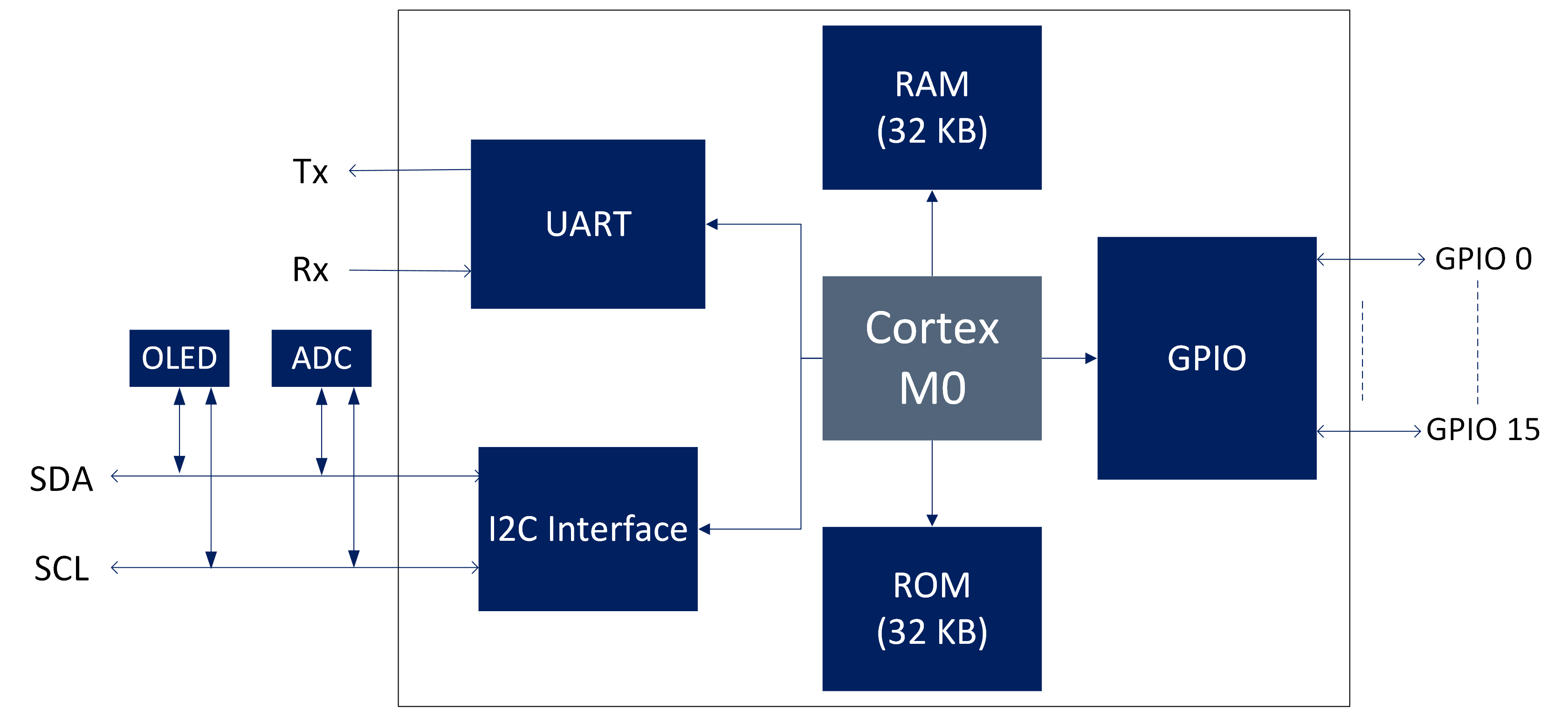

This area of 'interest' is for the hardware design ecosystem for Arm based System on Chip developments. This area is for discussion of design techniques. Specific design flow actions should be discussed in the design flow section.

Projects Using This Interest

Reference Design

Active Project

Competition 2025

Competition: Hardware Implementation

Collaborative

Active Project

Reference Design

Active Project

Collaborative

Case Study

Competition 2024

Competition: Hardware Implementation

Competition 2024

Competition: Collaboration/Education

Competition 2024

Competition: Hardware Implementation

Experts and Interested People

Members

Research Area

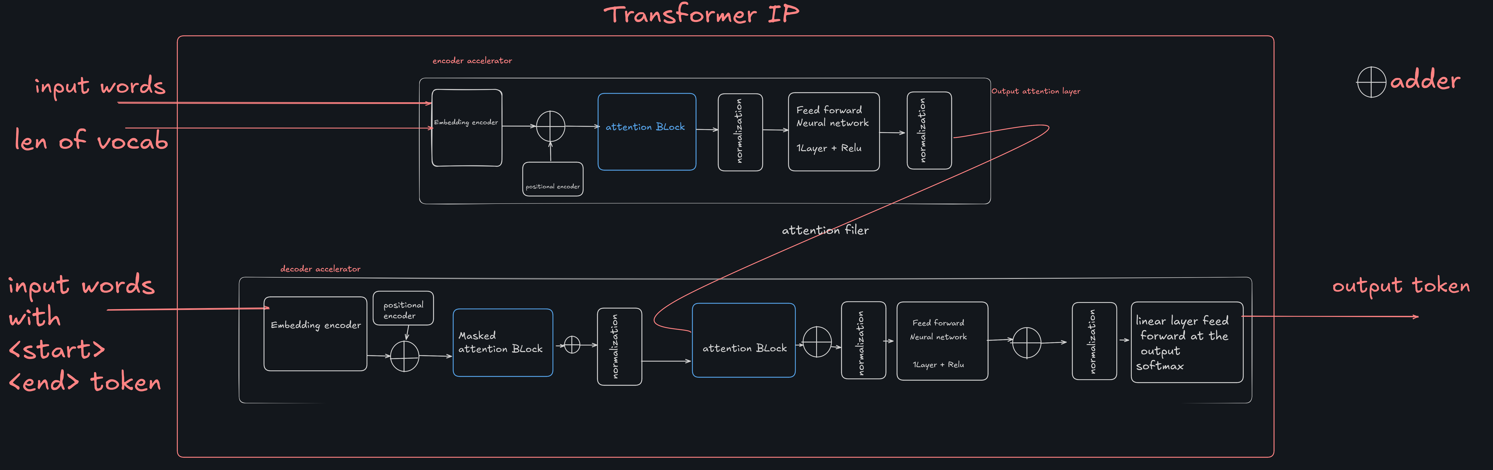

Deep neural networks hardware accelerators

Role

PhD Student

Add new comment

To post a comment on this article, please log in to your account. New users can create an account.