Synthesis

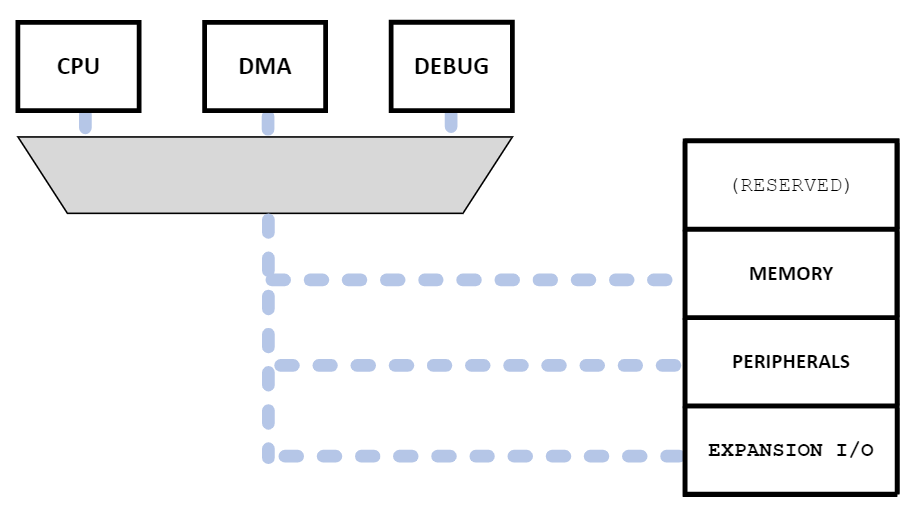

Is the process step to transform the technology independent register-transfer level (RTL) description of a system into a technology dependent netlist using a specific technology cell library.

Most Electronic Design Automation Synthesis tools support translation from designs written in SystemVerilog, Verilog, VHDL or a mixture of them.

Synthesis can be defined to optimise the output for different criteria, for example area use, timing, allowable loads on signals, the movement or merging of registers, or to control the amount of time a synthesis takes. Synthesis attributes and directives can be included in the source, for example to direct the synthesis to perform or not certain actions when synthesizing a design. Synthesis Attributes, such as expected arrival time of a signal at an input port, and Constraints, such as maximum input to output delay, are added to direct the synthesis.

Synthesis can be initiated from within an Integrated Design Environment by the designer or via a command interface that can be used to make scripts and automation of the process.

- Cadence - Genus

This step takes our verilog modules, and a liberty standard cell library and turns it into a netlist. A netlist is a functionally equivalent file to the verilog file but uses explicit declarations of cells, and the connections between them.

In Genus, the steps for synthesis are

- Load library files

- Read in verilog/HDL and elaborate design

- Read in constraints

- Synthesize to generic gates (i.e. not technology specific)

- Map gates to technology gates

- Optimisize netlist using constraints against the netlist

- Write reports on timing, power, area etc.

- Save and export netlist (Plus UPF, LEC files, and DFT files if needed)

An example script for genus synthesis can be found in our git repository

Projects Using This Design Flow

Experts and Interested People

Members

Related Project Milestones

| Project | Name | Target Date | Completed Date | Description |

|---|---|---|---|---|

| Fast-kNN: A hardware implementation of a k-Nearest-Neighbours classifier for accelerated inference | Synthesis |

Run synthesis and formal equivalence checks |

||

| Sensing for Precision Agriculture | Synthesis (97) |

Aim: Synthesis the digital component of our design (custom RTL + NanoSoC) Progress: Synthesised simple Verilog file with Cadence Genus and floorplanned with Innovus using the SKY130 PDK, documented. https://github.com/lewisMW/agriculture-SoC/issues/35

|

||

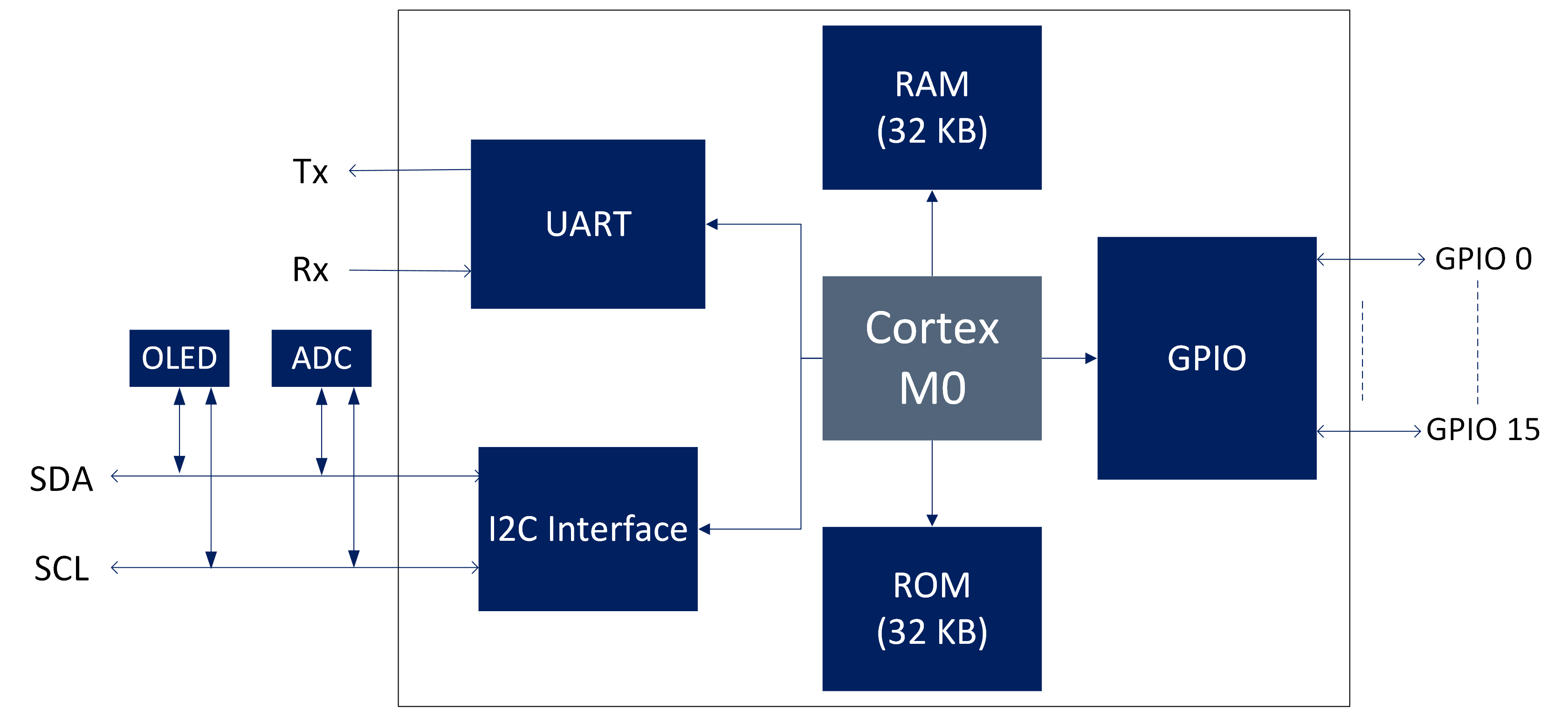

| ARM Cortex M0 Based SoC for Biomedical Applications | Synthesis |

In this milestone, we will use Cadence Genus to compile our design using 90 nm libraries. |

||

| Test draft | Synthesis |

Just testing preview |

||

| Aspen: A 630 FPS Real-Time Posit-Based Unified Accelerator for Extended Reality Perception Workloads | Synthesis (97) |

Add new comment

To post a comment on this article, please log in to your account. New users can create an account.