RTL Verification

Introduction

Is a 'design closure' stage to ensure independent register-transfer level (RTL) description of the system is consistent and ready for later stages of the design process.

Methods of Verification

The RTL description of the system can be deployed to an FPGA.

If a formal method approach is being used for the behavioural design task then proofs can be generated that show the design matches the specification for the system.

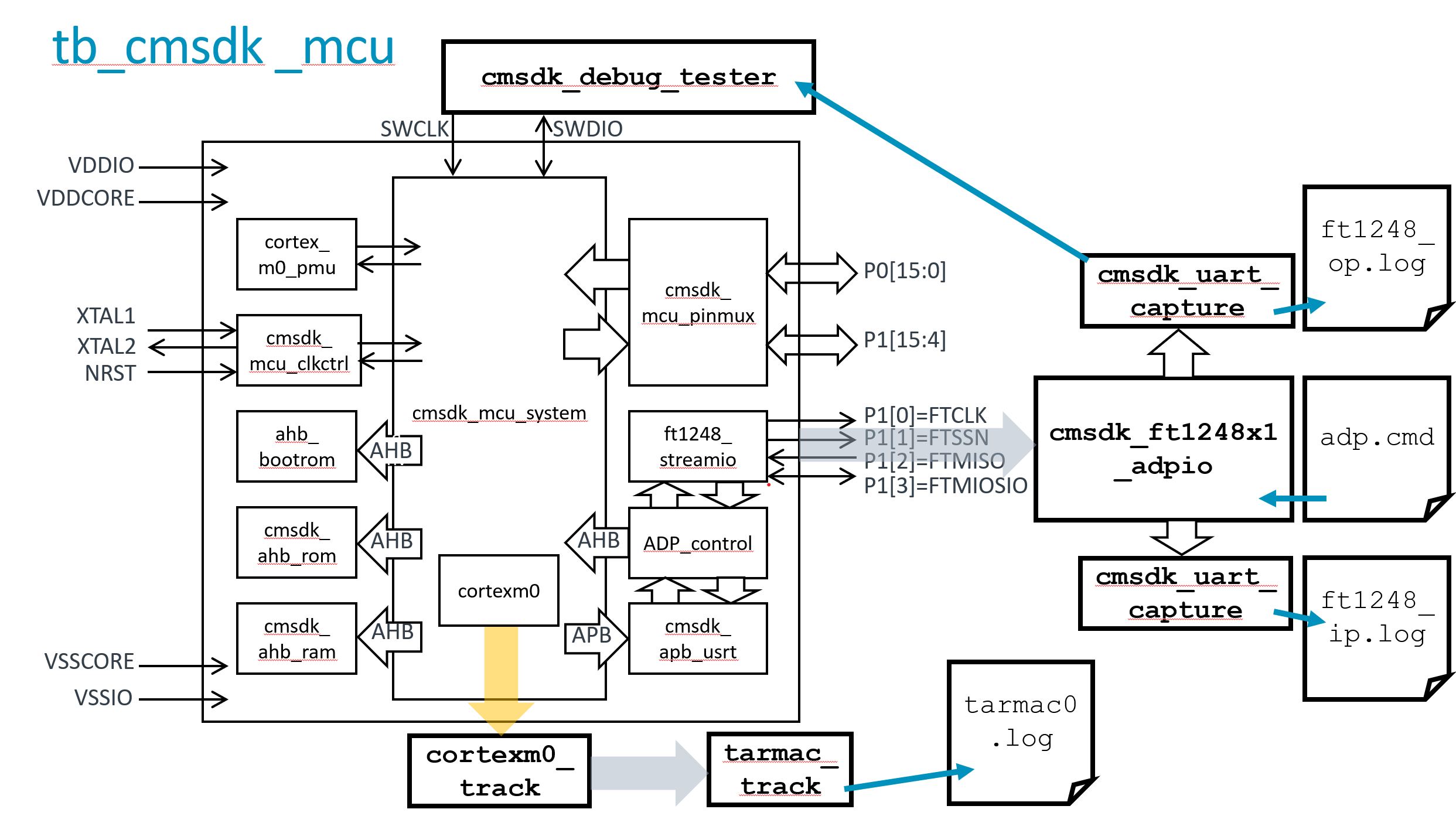

The RDL can be verified using test benches in a simulator environment. High level languages have constructs to aid the verification process, these generate the stimuli that are used to verify the RTL design descriptions in a simulation tool.

Projects Using This Design Flow

Experts and Interested People

Members

Related Project Milestones

| Project | Name | Target Date | Completed Date | Description |

|---|---|---|---|---|

| Battery Management System-on-chip (BMSoC) for large scale battery energy storage | RTL Verification |

|

||

| Arrhythmia Analysis Accelerator : A-Cube | RTL Verification (101) |

Implement the integration results in the ZCU104 FPGA board. |

||

| Arrhythmia Analysis Accelerator : A-Cube | RTL Verification (101) |

Test the hardware on the ZCU104 FPGA board. |

||

| Interference Detection and Mitigation Accelerator for Automotive Radar SoCs | RTL Verification (101) |

Verification using Xilinx Tool |

||

| Sensing for Precision Agriculture | RTL Verification (101) |

Aim: Verify our custom RTL + NanoSoC on an FPGA, with mock ADC input. Progress: 5x firmware tests simulated on NanoSoC. Found a bug with the RTC. https://github.com/lewisMW/agriculture-SoC/issues/33 https://github.com/lewisMW/agriculture-SoC/issues/36

|

Add new comment

To post a comment on this article, please log in to your account. New users can create an account.