SPI/QSPI

Serial Peripheral Interface (SPI)

SPI is one of the most common synchronous serial communication protocols for chip-to-chip communications. It is often used to communicate between a manager chip such as a microcontroller, and a subordinate chip such as off-chip memory, display drivers, or sensors. SPI can be configured to support multiple subordinate devices, either by the inclusion of multiple subordinate select pins, or by daisy chaining the data pins.

SPI typically uses 4 pins: a clock; a manager-in subordinate-out (MISO); a manager-out subordinate-in (MOSI); and a chip select pin. The manager initiates communication by driving the clock and then chip select pin low.

The maximum bandwidth of SPI is theoretically up to 60 Mbps over short distances, although practically this is likely to be lower.

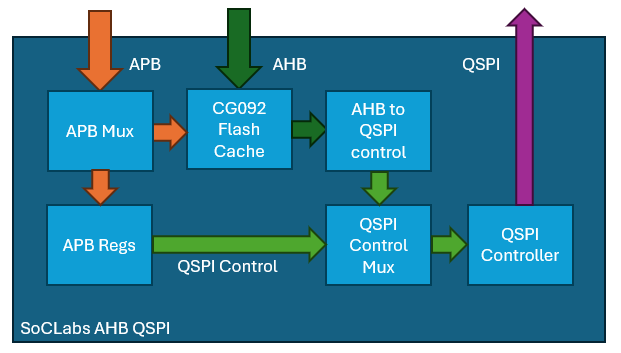

Quad Serial Peripheral Interface (QSPI)

QSPI is as an alternative to SPI and allows for higher bandwidths. Rather than having a single MISO and MOSI it has 4 bi-directional IO pins. This adds some overhead in the protocol as there is a delay for the bus-turnaround phase, but the protocol can achieve bandwidths of 240 Mbps.

Explore This Technology

Projects Using This Technology

Add new comment

To post a comment on this article, please log in to your account. New users can create an account.