View Active Collaborative Projects

Precision timekeeping is a foundational service in any distributed system. Whether synchronising Ethernet frames to a PTP grandmaster, timestamping die-to-die packet exchanges between chiplets, or scheduling time-critical hardware events, the system needs a clock that is accurate, capturable at multiple points simultaneously, and adjustable by both hardware servo loops and software without stopping.

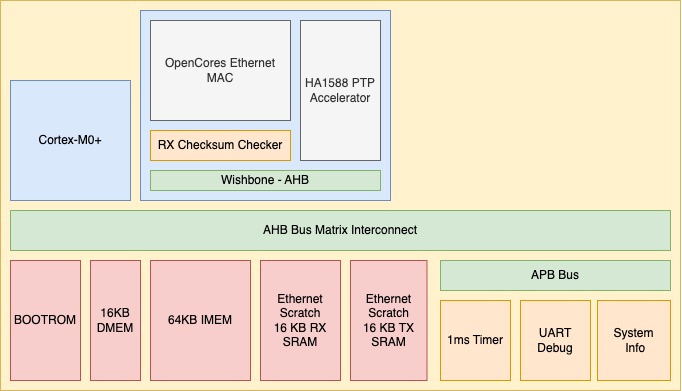

This program is dedicated to the development of a System on Chip (SoC) platform, specifically designed to support learning and research activities within Indonesian academic institutions. The platform serves as an educational and research tool for students, lecturers, and researchers to gain hands-on experience in digital chip design.

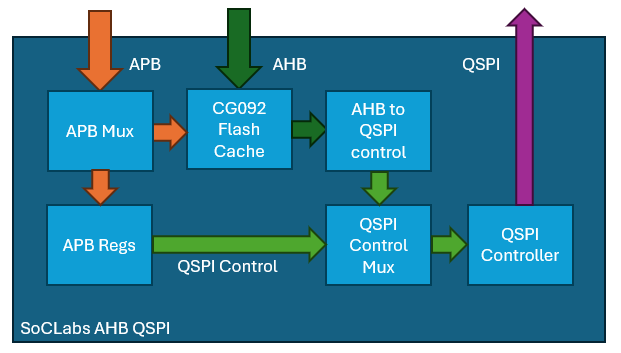

The instruction memory in the first tape out of nanosoc was implemented using SRAM. The benefit was the read bandwidth from this memory was very fast, the downside was on a power-on-reset, all the code was erased as SRAM is volatile memory. An alternative use of non-volatile memory would benefit applications where deployment of the ASIC does not allow, or simply time is not available for programming the SRAM after every power up.

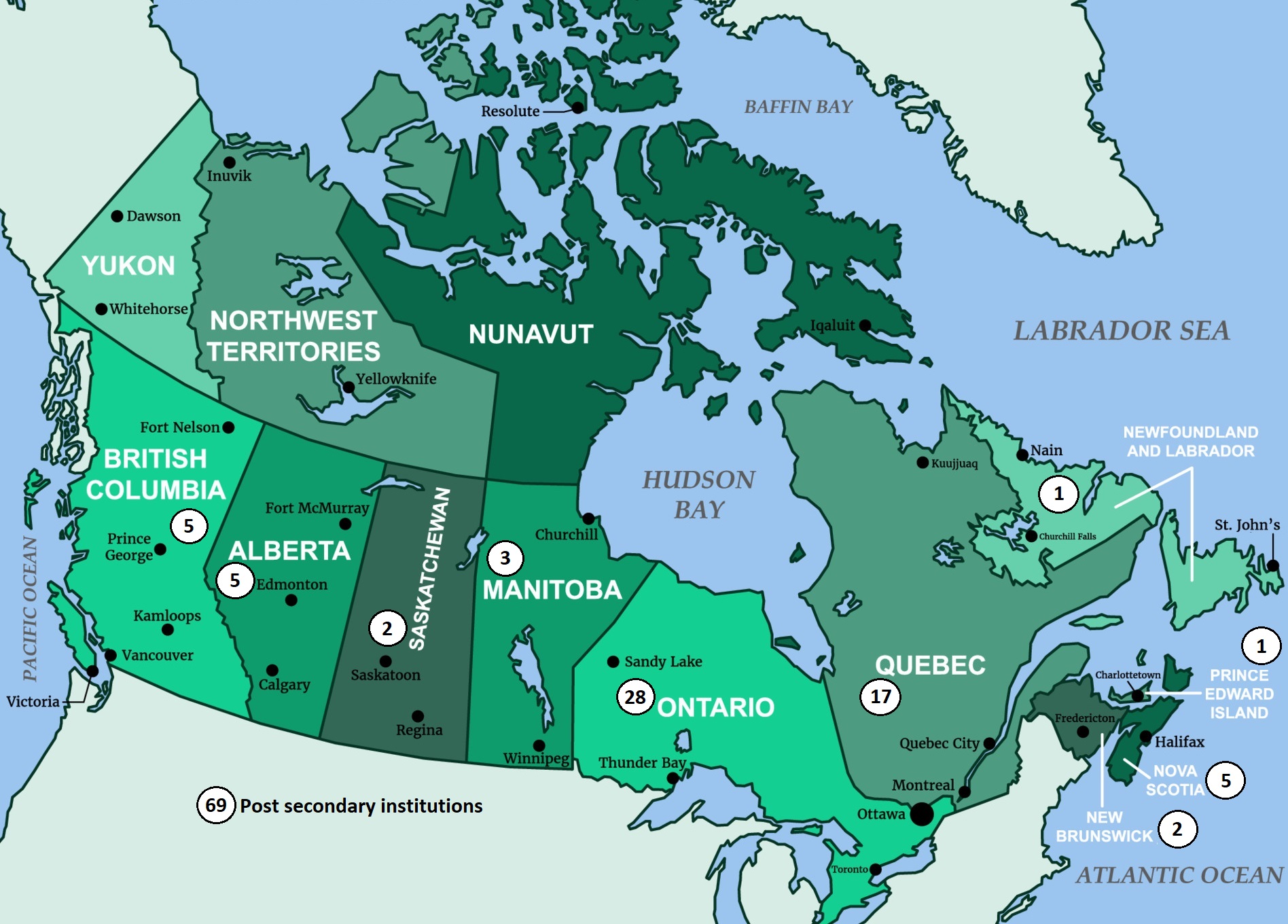

This collaboration project is aimed at providing specific tailored activities to the local geography in Canada by developing local actions that will help stimulate academics and their institutions and the broader semiconductor industry supporters to create new and exciting SoC design projects. It may include:

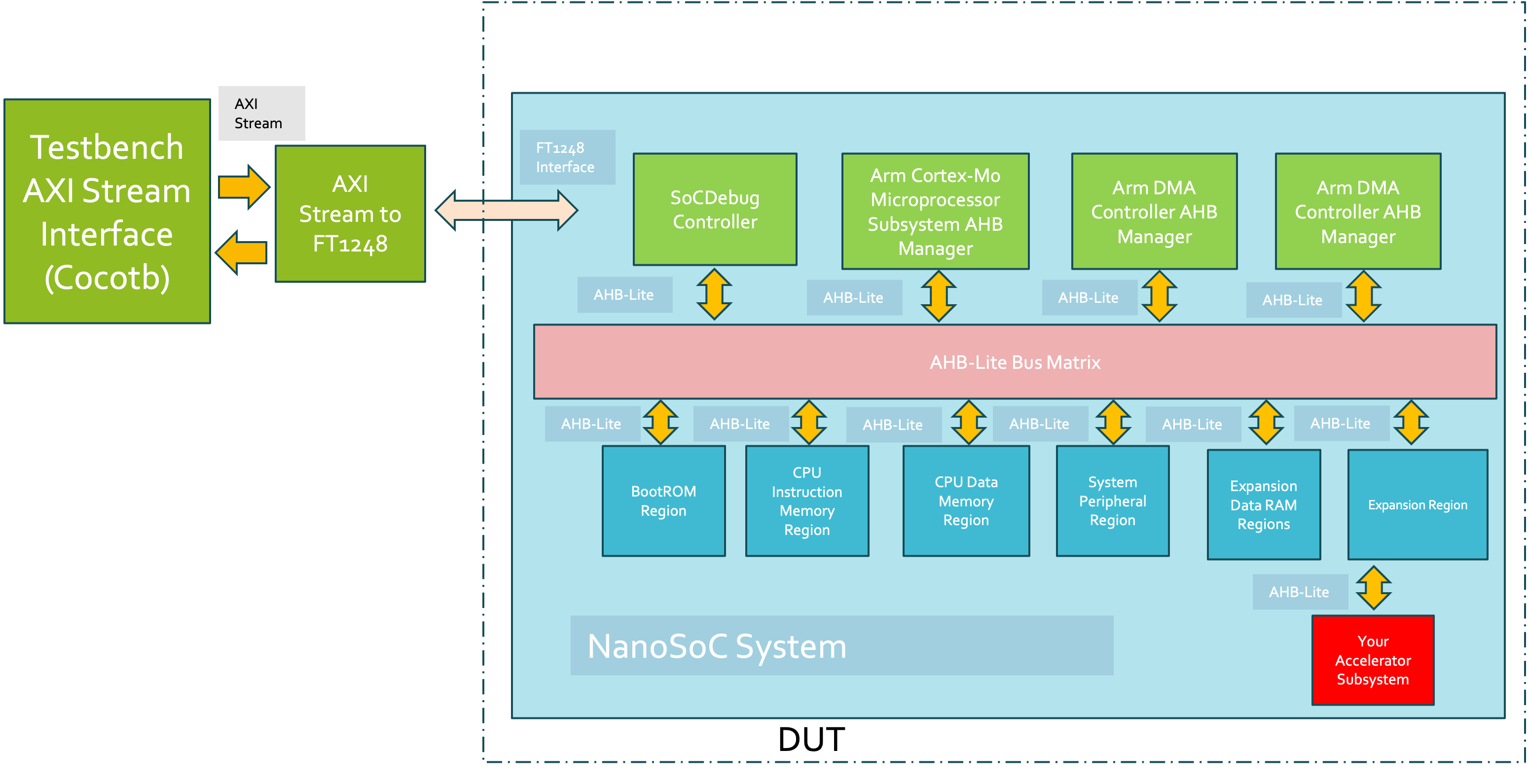

Performing system-level verification on a System-on-Chip (SoC) design is crucial for ensuring the correct function and overall performance of the entire system, rather than individual components. This project is aimed at developing the necessary resources and design flow stages for the verification of the NanoSoC reference design.

Architectural Design: Verification MethodologyWith NanoSoC, there are multiple options for performing system-level verification.

Motivation

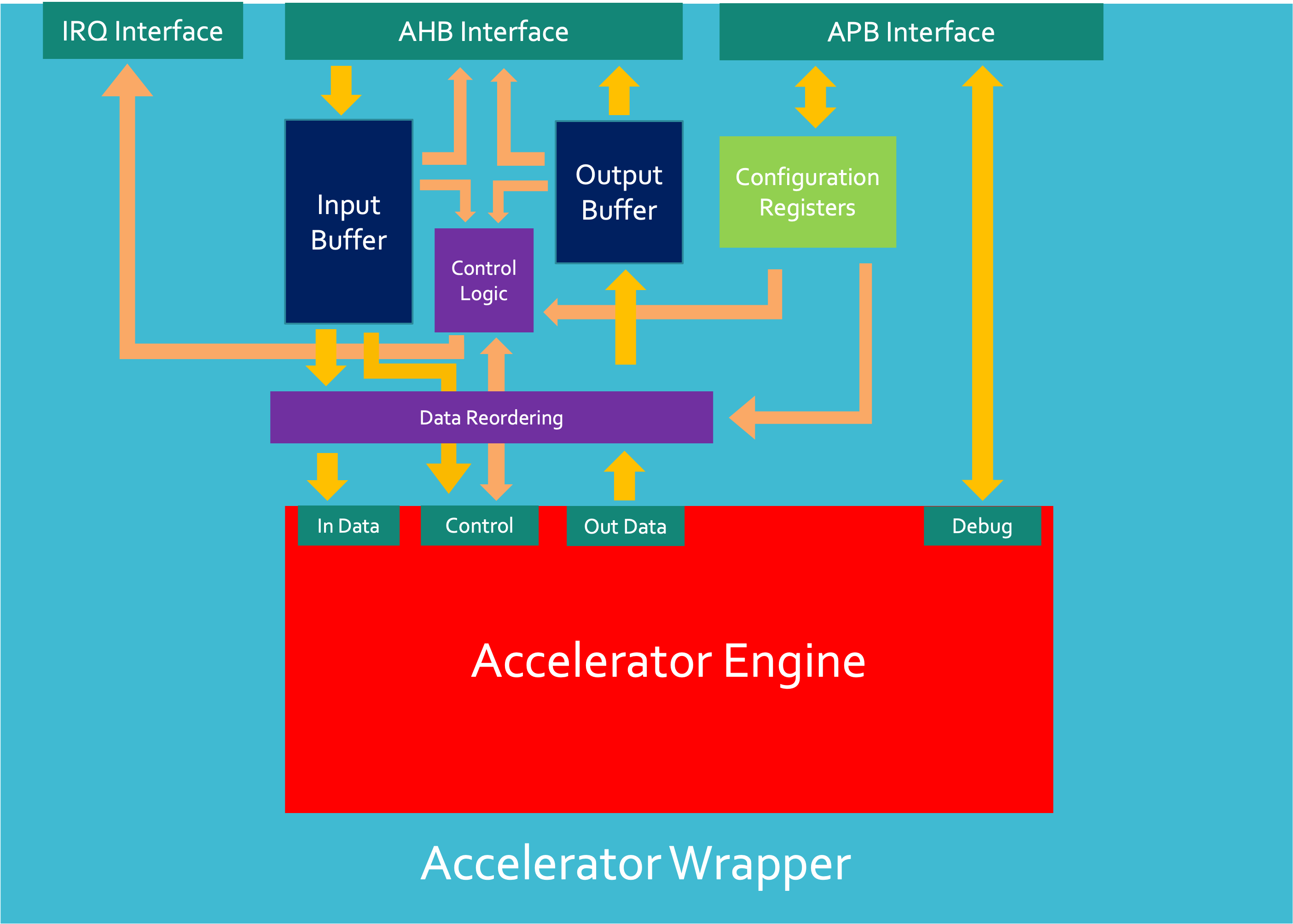

At SoC Labs, we have need of an accelerator to test our SoC infrastructure and confirmation of our accelerator wrapper design to get size and performance information as well as to try and get ahead and uncover potential problems researchers may experience trying to put their IP into the reference SoC.

Specification

The preliminary design has been broken into two main blocks:

David Mapstone

David Mapstone

Trio Adiono

Trio Adiono

Daniel Newbrook

Daniel Newbrook

John Darlington

John Darlington