This project aims to design and implement a high capacity memory subsystem for Arm A series processor based SoC designs. The current focus of the project is the design and implementation of a Memory Controller for DDR4 memory.

View Request of Collaboration Projects

The Synopsys HAPS® System adds additional capabilities to the FPGA-based prototyping environments SoC Labs can use to support projects. The HAPS® system provides a greater amount of logic resources supporting the development of larger SoC designs. It can be used to support multiple projects simultaneously. It is used by many semiconductor companies, including ARM, for their CPU verification. This collaboration project will use the HAPS® system in SoC Labs projects and share with the community experience in utilising such systems.

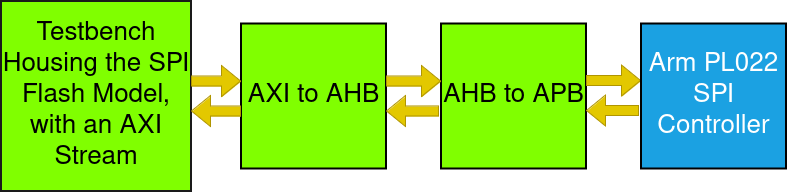

The Arm PL022 provides an interface for synchronous serial communication with peripheral devices connected to the SoC via the Advanced Peripheral Bus (APB). It supports a choice of interface operation, Motorola compatible Serial Peripheral Interface (SPI), National Semiconductor Microwire, or Texas Instruments synchronous serial interface. See the Techology page for details.

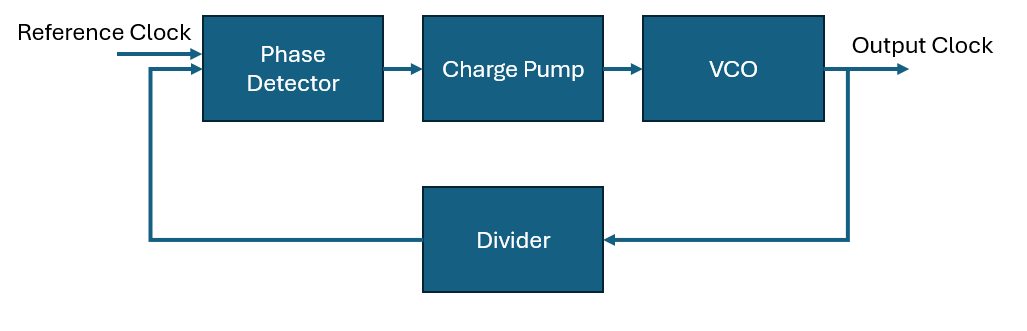

To design and verify a simple PLL for use as generator of clock signals in System on Chip design. The desired outcome from this project should be the following:

Clock generation for frequencies between 60 MHz and 1.2 GHzInclude PLL-lock signal for system start upLow clock uncertainty below 5% (transition time and jitter)Integer clock divider which can be updated at run timeMinimal areaThe resulting IP for these component blocks will be made available to the soclabs community for the upcoming design contest.

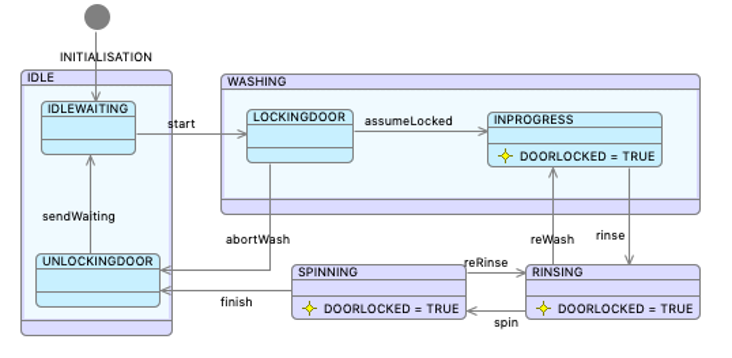

The aim of the project will be to establish the tool chain and flows to demonstrate Event-B refinement to a Register Transfer Level implementation that can target an FPGA implementation. Previous European, EC Information and Communication Technologies FP7 DEPLOY and European Union ICT Project ADVANCE developed VHDL code generation from Event-B models. A number of projects within these and other research programmes have looked at the required process flows. The Rodin Platform is an open source Eclipse-based IDE for Event-B.

Srimanth Tenneti

Srimanth Tenneti

John Darlington

John Darlington

Daniel Newbrook

Daniel Newbrook

Michael Butler

Michael Butler