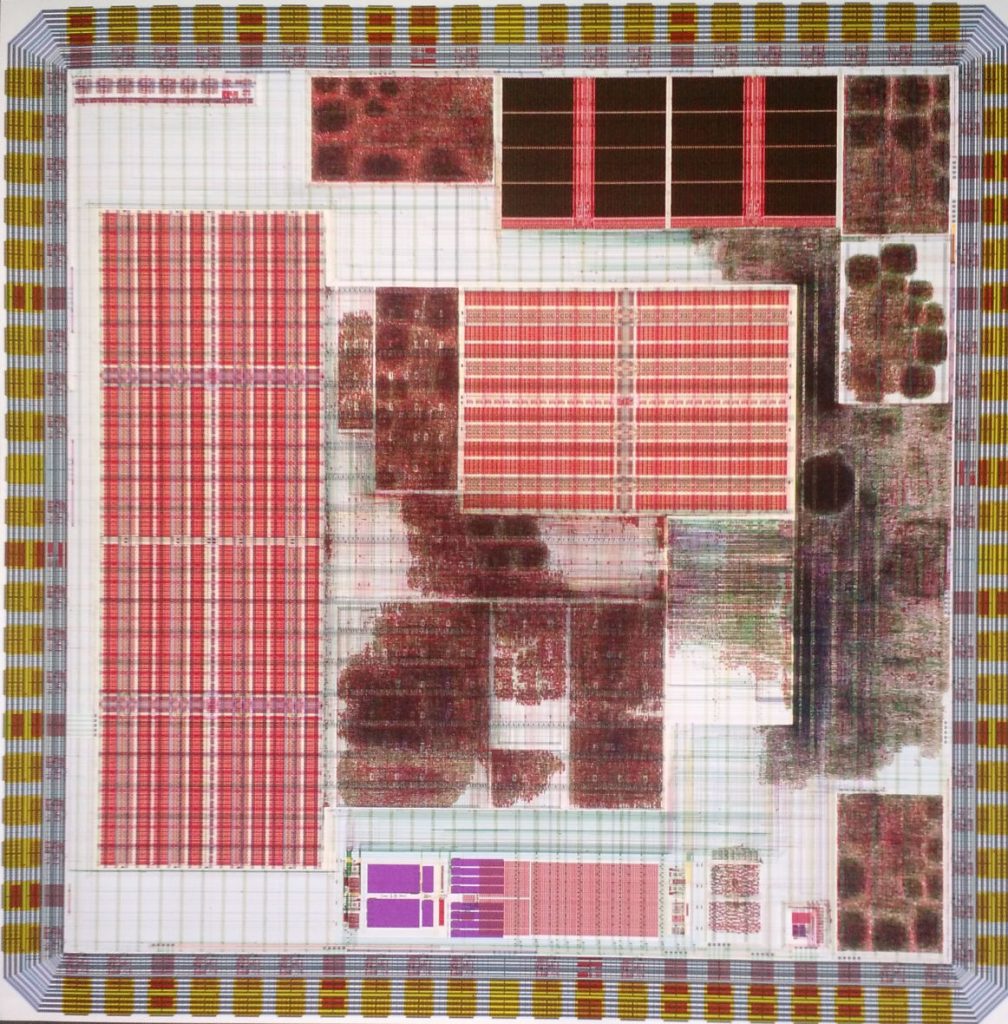

Pipistrelle-4 65nm low power multi-project SoC

Pipistrelle-4, is the latest in a series SoCs for demonstrating multiple student projects in low-energy systems. Various circuit/system ideas from multiple researcher focusing on energy and performance with optimised SRAM bitcell and low-area overhead energy-efficient flip-flops.

Previous chips in this series include;

Pipistrelle-3, with body-bias to improve performance at low voltage as well as an autonomous dynamic voltage and frequency scaling (DVFS) control state machine for carefully sequencing clocks, regulator settings and body-bias. Additional integration of the switched-capacitor regulator and harvester has been made possible by adding numerous low–power oscillators along with further efficiency improvement and a reverse current protection scheme.

Pipistrelle-2, with low power clock sources, an important part of a minimum energy system for driving CPUs, switched-capacitor converters, power-management unit logic, wake-up timers and more. This chip takes the first step to prototyping suitable fully-integrated oscillator topologies, as well as improving on previous versions of SRAM, power and energy harvesting converters.

Pipistrelle-1, a platform SoC for experimenting with various energy and power management algorithms and techniques for wireless sensor networks. Used to demonstrate sub threshold power conversion and energy harvesting techniques.

Add new comment

To post a comment on this article, please log in to your account. New users can create an account.