Competition 2024

Competition: Collaboration/Education

IMPLEMENTATION OF FIXED TIME BASED TRAFFIC LIGTH SYSTEM USING FPGA WITH VERILOG HDL.

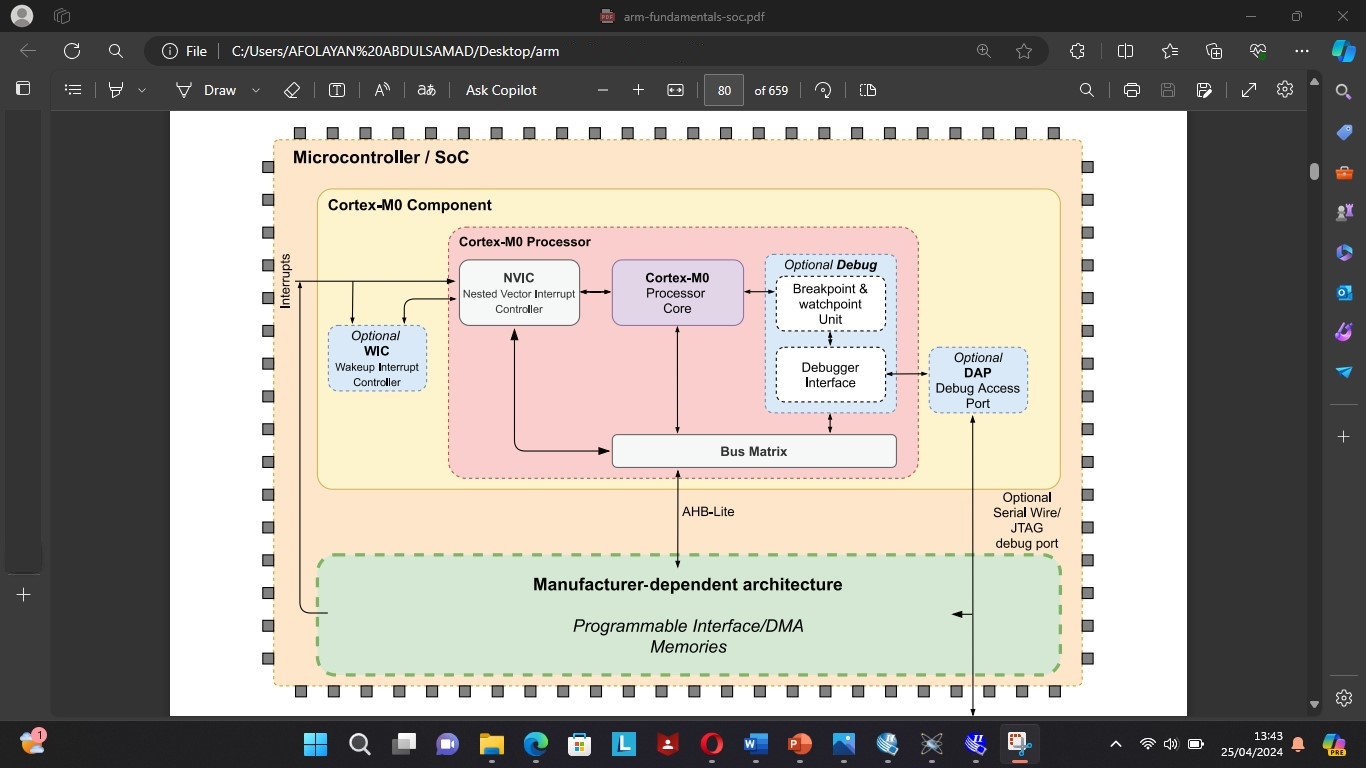

This Project is to develop traffic light system that can reduce traffic congestion with the aid of counters for each lane and acts wisely with the intersection in real time based with a fixed time constrain, include both hardware and software requirements using SOC FPGA technology with fundamental specification for the Register Transfer Level (RTL).

Project Milestones

Complete

In Progress

Not Started

Not Needed

Click on any milestone above for details

X

Do you want to view information on how to complete the work stage ""

or update the work stage for this project?

-

FPGA SoC prototyping with Xilinx(R) PYNQ(R) platform

Target Datefamiliarize with the CAD tool.

-

Architectural Design

Design FlowTarget Datestructural design of the project

-

Behavioural Design

Design FlowTarget Datefunctional design of the system

-

Simulation

Design FlowTarget Datethe system imitating the rea world scenarios.

-

Behavioural Modelling

Design FlowTarget Dateabstract representation of the system

-

Design for Test

Design FlowTarget Dateverification of the system based on the requirements.

-

Milestone #7

Target Date -

Milestone #8

Target Date -

Milestone #9

Target Date -

Milestone #10

Target Date -

Milestone #11

Target Date -

Milestone #12

Target Date -

Milestone #13

Target Date

Team

Name

Research Area

FIELD PROGRAMMABLE GATE ARRAYS

Role

STUDENT

AFOLAYAN, ABDULSAMAD

AFOLAYAN, ABDULSAMAD

Cortex-A7

Cortex-A7

Add new comment

To post a comment on this article, please log in to your account. New users can create an account.