Arm Cortex-M0 microcontroller

Example Microcontroller

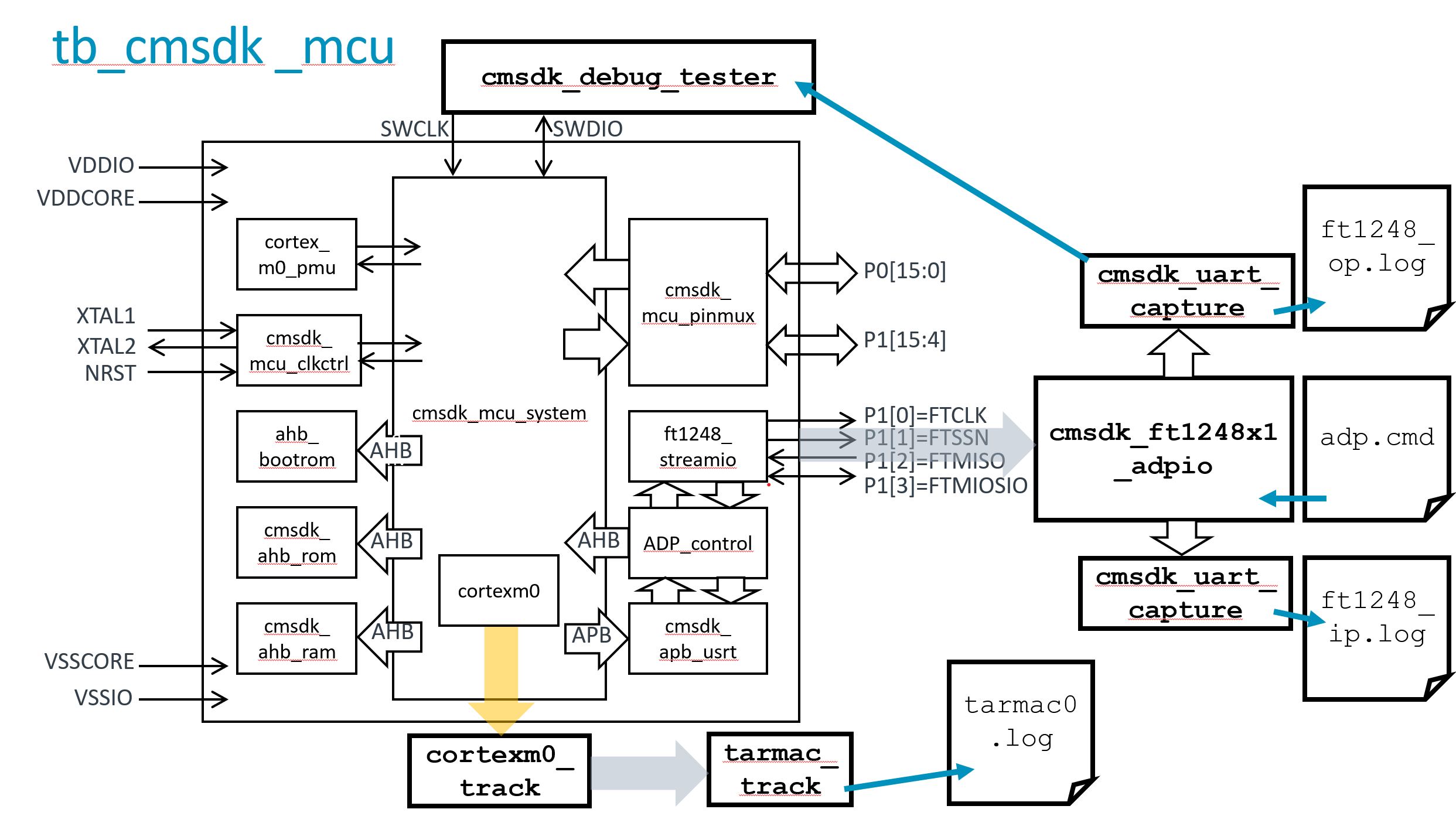

This example design is based on the Arm Cortex-M System Design Kit (CMSDK) reference design.

This is a good starting point with example CPU configuration plus on-chip memory and basic General Purpose Input/Output (GPIO) and Serial Communications (UARTs) peripherals; a full set of example test programs is provided together with Serial-Wire embedded debugger channel access. Together with the documentation provided the baseline system can be validated and then extended and modified as required.

The Arm example provides a baseline design for developing an application- or project-specific embedded controller; there are a number of adaptations and enhancements over the Arm CMSDK baseline design:

- "Tarmac" disassembler support has been moved to the top-level testbench and supports both RTL and gate-level Cortex-M0 CPU tracing. Uses an RTL "tracking" model to rebuild RTL state externally based on CPU input stimulus.

- An experimental ASCII Debug Controller has been added as a Direct Memory Access bus manager that allows AMBA-AHB diagnostic access on-chip with read/write/initialize and data upload capabilities.

- An experimental serial interface module that uses the Future Technologies (R) FT1248 communication protocol that supports arbitrary SoC clock rates, and supports direct communication to a Host USB channel using an FT232H IC or module free of any baud-rate clock dependencies. Implemented as 1-bit data, (4-bit interface) serial interface on GPIO port-1 bits[3:0].

- An FT1248 test-bench behavioral controller that reads and transfers an optional ADP command file (adp.cmd), and formats serial data streams to log both input (ft1248_ip.log) and output (ft1248_op.log) text log files re-using the Arm 'cmsdk_uart_capture.v" module instantiations. (The output module supports control enable of the 'cmsdk_debug_tester' testbench module as well as the original UART2

- A new MCU top-level module 'cmsdk_mcu_chip.v" module is replaces the original 'cmsdk_mcu.v" and this instantiates generic I/O pad driver and supply-port modules for all inputs & output to allow technology-specific mapping for ASIC or FPGA implementation.

- The boot monitor and run-time software code is modified to use a 'cmsdk_apb_usrt' module that is a modification of a standard 'cmsdk_apb_uart' but with serial IO replaced by AXI stream ports for transmit and receive byte data, maintaining software compatibility with the standard UART device drivers.

Directory and IP structuring

The following IP bundles are required from the AAA Product Download Hub portal:

- Corstone 101 (Product ID: BP306-GRP)

- Cortex-M0 CPU (Product ID: AT510-GRP)

- DMA-230_MicroDMA_Controller_IP (Product ID: PL230-r0p0-02rel2-1)

Release Notes and ReadMe documentation are provided to guide through unpacking these deliverables into individual directories

Although the Arm IP deliverables expect licensees to develop within the directory trees provided, for best practice it is highly recommended that the Arm IP is treated as Read-Only Libraries and all development takes place external to this in a user working directory tree.

This is important in order to ensure that version control systems and project sharing (within or across academic institutions and partners) do not 'check in' or publish the proprietary Arm IP files and designs inadvertently.

So it is strongly recommended to unpack all the Arm AAA deliverables into a top-level directory ( arm-AAA-ip-installed/ for example).

A soclabs example development tree is provided as a gitlab project. This is delivered as a directory named soclabs-cortexm0-mcu/ and a soft-link named arm-AAA-ip should be provided at this same level of filesystem hierarchy pointing to the arm-AAA-ip-installed directory.

Providing the development tree is of the form:

- arm-AAA-ip -> arm-AAA-ip-installed/Corstone 101/.... (link to the read-only 'external' data)

- soclabs-cortexm0-mcu/Cortex-M0/... (read-write active development tree)

then the Arm IP files can all be accessed by relative pathnames to build and simulate correctly.

The basic getting started instructions are provided here

Design Documentation

The primary documentation is provided in the Arm deliverables, namely:

- arm-AAA-ip/Cortex-M0/*.pdf

- arm-AAA-ip/Cortex-M0/AT510-BU-00000-r0p0-03rel3/doc/*.pdf

- arm-AAA-ip/Corstone-101_Foundation_IP/*.pdf

- arm-AAA-ip/Corstone-101_Foundation_IP/BP210-BU-00000-r1p1-00rel0/documentation/*.pdf

- arm-AAA-ip/DMA-230_MicroDMA_Controller_IP/PL230-BU-00000-r0p0-02rel2/docs/*.pdf

The soclabs example has been modified slightly to move the (optional) DMA controller up to the top-level 'mcu' of the design to enhance the diagnostic infrastructure for uart output capture and CPU core disassembler support at the testbench level.

The somewhat deep working directory structure has been chosen to match the Arm reference design example so that the hierarchy matches closely the documentation, and only the necessary verilog and test code (C and assembler) files are populated in the development tree. Any files modified from the Arm deliverables have an additional comment added to the file header.

The example design provided can be located in the 'systems' subdirectory:

- soclabs-cortexm0-mcu/Cortex-M0/soclabs_demo/systems/cortex_m0_mcu

To help get up to speed efficiently with this example, a browsable HTML documentation tree is provided (in tgz compressed form):

- soclabs-cortexm0-mcu/Cortex-M0/soclabs_demo/systems/cortex_m0_mcu/v2html_doc.tgz

Which unpacks to:

- soclabs-cortexm0-mcu/Cortex-M0/soclabs_demo/systems/cortex_m0_mcu/v2html_doc/

- open soclabs-cortexm0-mcu/Cortex-M0/soclabs_demo/systems/cortex_m0_mcu/v2html_doc/hierarchy.html in preferred web browser

This is built with the v2html tool, © 1999-2009 Costas Calamvokis

Simulation Environment

The working directory for RTL simulation is to be found at:

- soclabs-cortexm0-mcu/Cortex-M0/soclabs_demo/systems/cortex_m0_mcu/rtl_sim

To build an run simulations both an RTL simulator and and Arm software tools are required

Seats of Arm Development Studio 'Gold' are included in the AAA entitlements. Once installed the appropriate command line tools can be run with the makefiles provided:

In the environment set up at the University of Southampton (link) the arm tools environment is simple configured as:

- export ARM_PRODUCT_PATH=/apps/arm/developmentstudio-2021.0/sw/mappings

- export ARM_TOOL_VARIANT=gold

- export PATH=$PATH:/apps/arm/developmentstudio-2021.0/sw/ARMCompiler5.06u7/bin/

The Arm Corstone-101_Foundation_IP/BP210-BU-00000-r1p1-00rel0/documentation Example System Guide and Technical Reference Manual describe the set up for simulation tools.

When the tools are configured, basic out-of-box testing, using the simple 'hello.c" (or another test from the `../testcodes/` directory) test program,

- make code TESTNAME=hello (build the ROM code image to execute)

- make compile (compile the RTL MCU and testbench for simulation)

- make run TESTNAME=hello (run the simulation using specific pre-compiled ROM code, or make sim for interactive waveform simulation)

Team

Initial Prototype Project for:

David Flynn

David Flynn

Cortex-M0

Cortex-M0

Comments

Release version of Cortex-M0 IP

I am trying follow the getting started page from the project's gitlab repository. When I try to download the IP for the Cortex-M0, I can only find the AT510-r0p0-03rel2-1 version not AT510-BU-00000-r0p0-03rel3 which is used by the project. As a result, when I run "make compile-mti, I get error messages, because the AT510 IP cannot be found.

Should I modify the file paths in the tbench_M0.vc file to accommodate the differences in the AT510 IP versions? Where could I find the rel3 version of the IP?

Cortex-M0 IP paths

It looks as if the AAA Cortex-M0 deliverables were updated in the Southampton site and the paths do need to be repaired in tbench_M0.vc as you suspected.

I have had a quick look at the installation and it appears as if :

.../aaa-ARM-ip/Cortex-M0/AT510-BU-00000-r0p0-03rel3/

may now be referenced using the updated "version independent" path

.../aaa-ARM-ip/latest/Cortex-M0/

similarly the Corstone-101 IP:

...aaa-ARM-ip/Corstone-101_Foundation_IP/BP210-BU-00000-r1p1-00rel0/

to

.../aaa-ARM-ip/latest/Corstone-101/

and the PL230 micro-DMA:

.../aaa-ARM-ip/DMA-230_MicroDMA_Controller/PL230-BU-00000-r0p0-02rel2/shared/

to

.../aaa-ARM-ip/latest/DMA-230/

I do hope this works for you - and the explicit relative path issues, inherited from Arm CMSDK are addressed by setting clean environment variables in the nanosoc deliverables

Cortex-M0 IP paths

Hi David, I still have no access rights to the IP installed on the SoCLabs servers, so I had to download and unpack the IP myself from Arm's Product Download Hub. I modified the paths in tbench_M0.vc and the errors were eliminated. Once, I get access rights to the IP library installed on the server, I will try again with the original testbench file.

Cortex-M0 file paths

Sorry this is not straightforward. I have checked in the new preferred "/latest/" link paths into the repository so these should be ready when you have Southampton server access.

In the meantime, would you be happy to add a few more symbolic links to your installation of AAA IP bundles under the "arm-AAA-ip" directory you have built? If you create a directory at the top level named "latest" and then in that directory build symbolic links that match the new preferred pathnames then I think you should be able to make progress.

for example for Cortex-M0 CPU, but similarly for Corstone-101 and DMA230...

in arm-AAA-ip/latest/ directory, create a soft-link something like :

ln -s ../Cortex-M0/AT510-r0p0-03rel2/AT510-BU-50000-r0p0-03rel2 Cortex-M0

(or similar - such that ls -al shows your "latest/Cortex-M0" now points to the directory in the Arm IP that includes the logical verilog IP directory. And confirm this by listing what is visible at arm-AAA-ip/latest/Cortex-M0/logical/ )

This should then remove exact bundle part numbers and be ready for full server access when you can switch your link to the managed AAA IP repository

Cortex-M0 file paths

Many thanks for the help, I pulled the last commit into my forked repository and I successfully managed to create the symbolic links as suggested. However, I was still getting 2 errors for the DMA-230 IP. It turns out that the cause of the error is that the IP is placed under

DMA-230/shared/logical/pl230_udma/verilog/DMA-230/logical/verilog/but I suppose you might have arranged things differently on the SoCLabs server.Add new comment

To post a comment on this article, please log in to your account. New users can create an account.