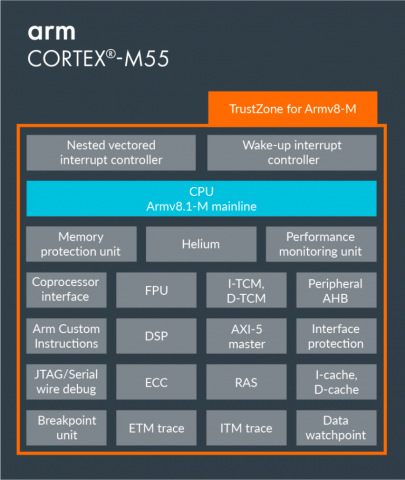

Cortex-M55

The Cortex-M55 implements the Arm v8.1-M Mainline architecture with a four stage in-order integer pipeline and M-profile Vector Extension (MVE) benefitting machine learning and signal processing applications. MVE has 8 vector registers of 128-bit width for Helium instructions and Custom Instructions for external co-processor accelerators.

Like the M7, the M55 has a two-level memory system with tightly-coupled memory blocks for real-time low latency applications.

The Nested Vector Interrupt Controller (NVIC) supports up to 480 interrupt inputs from peripherals with between 8 and 256 levels of priority.

TrustZone support for a Secure and a Non-secure state. The Secure and Non-secure Memory Protection Units (MPU) support up to 16 regions.

The bus mechanism provides an AMBA5 AXI interface for 2nd level memory, AMBA5 AHB external interface and AMBA4 APB debug interface.

Explore This Technology

Add new comment

To post a comment on this article, please log in to your account. New users can create an account.