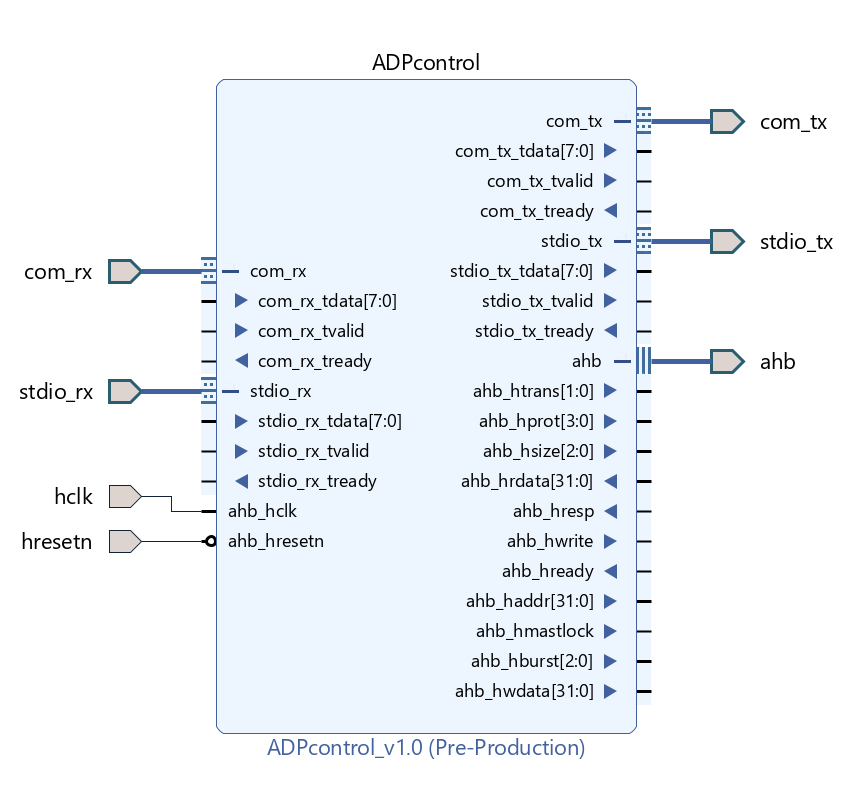

Hardware SoC bus level debug agent (v4)

A 'bare-metal' hardware debugger IP component that supports memory-mapped read, write, and file upload services before any microprocessor or systems IP and software are integrated and functional. Fully deterministic timing also supports using the interface for test vectors for both verification and SoC testing.

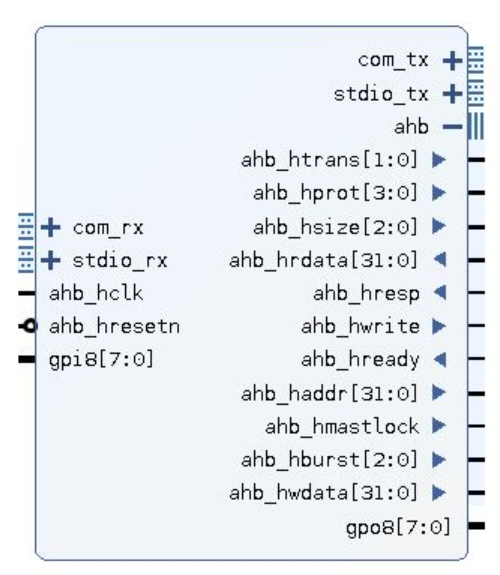

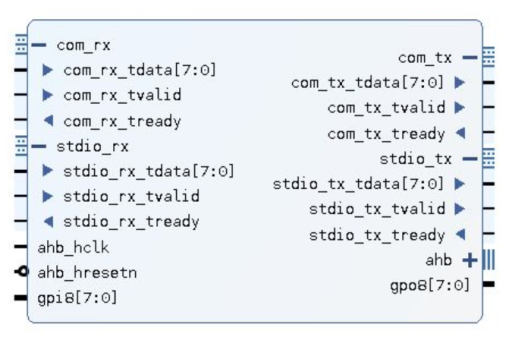

The component presents a bidirectional communications interface off-chip, using AMBA AXI-stream receive and transmit channels, an AMBA AHB-lite bus controller to the SoC memory mapped interconnect, and also provides AMBA AXI-stream STDOUT and STDIN channels to host processor or cluster.

A set of eight general purpose input and output ports can be used for system-specific signal monitoring and control. (the nanosoc design uses this to allow reset assertion to the CPU subsystem so that new code can be downloaded and the MCU rebooted.

AHB-lite initiator interface

The controller only does single transaction reads and writes - no burst accesses supported at this stage.

External RX/TX comms port

The port functionality is:

- com_rx : 8-bit external comms port data in (forward to STDIN and/or ADP monitor input)

- com_tx : 8-bit external comms port data out (forward from STDOUT and/or ADP monitor output)

- stdio_rx : 8-bit internal console port data in (from STDOUT)

- stdio_tx : 8-bit internal console port data out (to STDIN)

The use of AXI-stream interfaces supports basic byte-stream abstraction interfaces to application-dependent I/O devices, that may be serial or parallel:

- UART TX/RX interface; there are good open-source examples available such as:

- FT1248 RX/TX master interface; actively testing a soclabs prototype for this FTDI proprietary protocol which allows an arbitrary/variable clock source on chip to enable communication with a standard USB comms port without the fixed-baud-rate requirements of UARTs. FT1248 Dynamic Parallel/Serial Interface Basics (ftdichip.com)

- Byte-wide memory mapped stream channel interfaces - developed in the Xilinx Vivado FPGA platform to support a UART-compatible register set for fast TX/RX communication with full hardware handshaking, but designed for standard SoC integration.

[The ADP controller and FT1248 interface controller and AXI-to-stream-io (to 8-bit AXI-stream channels) are published in the the nanosoc re-usable MCU platform | SoC Labs project]

ADP functionality

The ASCII Debug Protocol engine allows a standard full-duplex communication channel (for STDIO etc) to support a diagnostic mode of operation (entered with an "escape" sequence) that provides:

- A version banner (2023 release: "50c1abs04")

- A user prompt (default ']' character)

- Echoed after an "ESC" char (0x1B) triggers entry to ADP monitor

- responds to a basic set of commands, the most basic being:

- "A <hex string parameter>" to set address base pointer

- "R <hex string parameter>" to read N 32-bit data values from current address pointer (autoincrementing word address +4)

- "H <hex string parameter>" to read N 16-bit data values from current address pointer (autoincrementing half-word address +2)

- "B <hex string parameter>" to read N 8-bit data values from current address pointer (autoincrementing byte address +1)

- "W <8-nibble hex string parameter>" to write a 32-bit data value to current address pointer (and autoincrement word address +4)

- "W <4-nibble string parameter>" to write a 16-bit data value to current address pointer (and autoincrement half-word address +2)

- "W <2-nibblehex string parameter>" to write an 8-bit data value to current address pointer (and autoincrement byte address +1)

- "Q" (or <Ctrl-D>) exit debug monitor mode (revert to standard input/output channels)

- plus some more advanced features:

- "V <hex string parameter>" to set a 32-bit Value (for fill or poll commands)

- "M <hex string parameter>" to set a 32-bit Mask value (for poll commands)

- "F <hex string parameter>" to fill a block of memory on N words (autoincrementing the address pointer) with Value V

- "P <hex string parameter>" to poll address up to N times (no address increment) (location and Mask == Value)

- "C <hex string parameter>" set user-GPO control flags (SoC specific)

- "S <hex string parameter>" send 8-bit char to SoC 'stdin' channel

- "U <hex string parameter>" Upload N-bytes of binary character stream and write to memory (incrementing byte address)

- Any std-output traffic from the system on chip is transmitted and quoted ('<' & '>') to between ADP commands while in debug mode

A simple Python "terminal program" provides full-duplex interaction interface (with an example developed with the Xilinx 'PYNQ' development environment as Jupyter notebook).

Success/Failure signalling

ADP reports the command executed or the results, and adds a " " space prefix if successful or a "!" prefix if failed to complete. For example:

- A bus read or write operation that gets a bus fault signals an error on the read or write response

- A poll operation either reports the number of polled operations until the masked value matches with the value set

- or reports a failure (time-out) if the poll count is reached and no match detected

- A Send character to std-input channel that cannot be posted (buffer or FIFO full or CPU not running) reports an error

David Flynn

David Flynn

Debug & Trace

Debug & Trace Debugging

Debugging

Comments

Work in progress - FPGA prototyping stage

Lots more information to follow

Work in progress - FPGA prototyping stage

Thanks David for providing this extremely useful protocol. The ASCII debug controller you shared offers a great balance between user interaction and simplicity, which is no small features. Your contribution is truly appreciated.

Add new comment

To post a comment on this article, please log in to your account. New users can create an account.