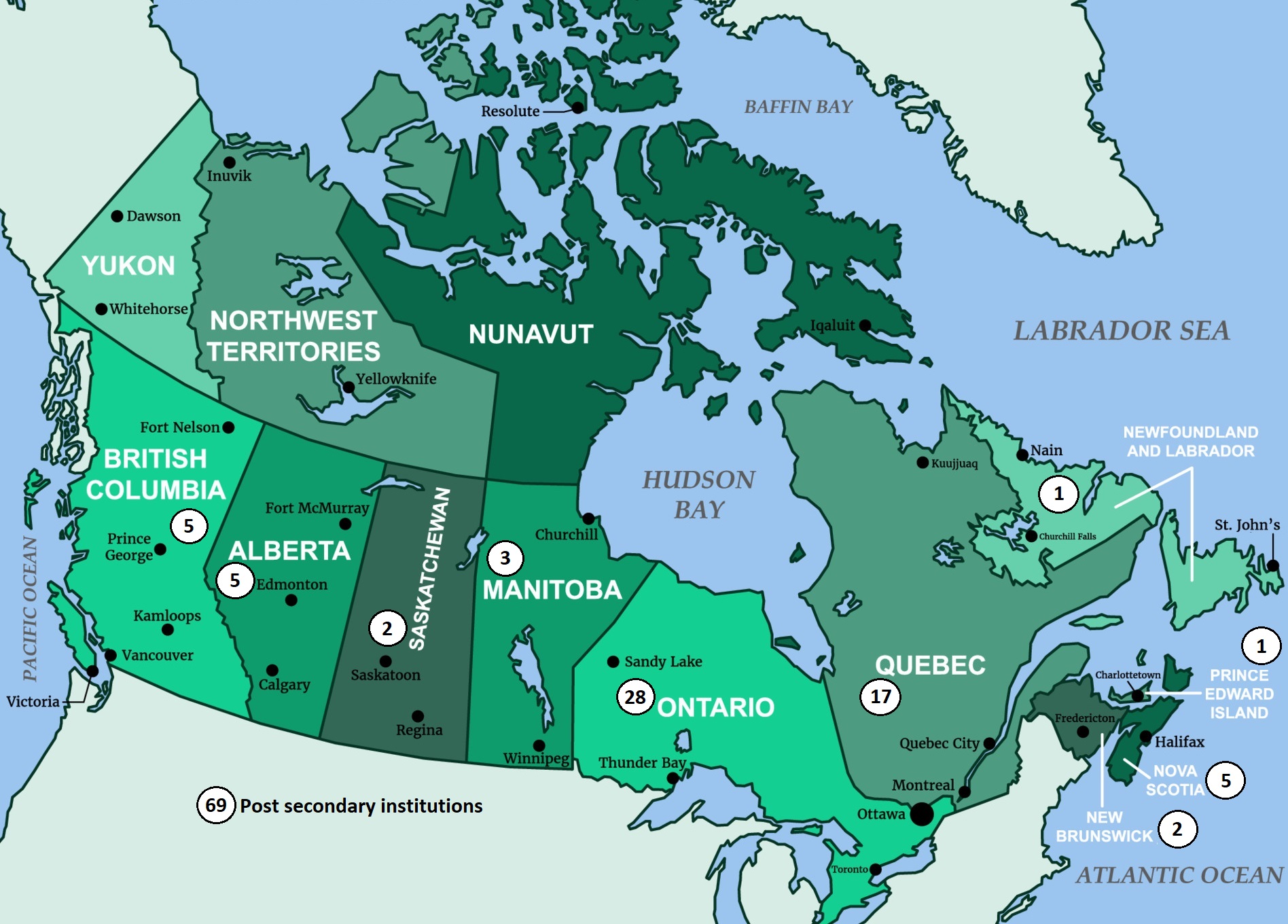

Geographical support for Canada

This collaboration project is aimed at providing specific tailored activities to the local geography in Canada by developing local actions that will help stimulate academics and their institutions and the broader semiconductor industry supporters to create new and exciting SoC design projects. It may include:

- holding specific local physical meetups where people can exchange design ideas

- utilising locally provided routes to fabrication.

- sharing hard to locate test capability across academic institutions.

There are many other potential opportunities for local collaboration and we hope this project will stimulate many over time. Hopefully the community will update the project as plans for activities develop so if you are local, please join the project and keep both in touch and involved.

Welcome to 2026 activities:

- To start the year we are hosting a free online workshop on Simplifying System-on-Chip (SoC) design and fabrication.

- The geography specific design contest SoC Design Contest 2026 for Canada and the America's in collaboration with Arm and CMC is still open.

Prior activities:

- The 2024 Canadian Semiconductor Symposium, took place October 9 and 10 in Markham, Ontario.

- Webinar, Thursday 17th Oct, Make Academic System on Chip Projects Easy via Collaboration and Reusable Design. How the broad range of IP freely available via Arm Academic Access combined with academic-focused reusable reference designs and tape out flows are making System on Chip projects easier to undertake by individual students and larger academic teams. Examples of projects being developed by the SoC Labs academic community. A specific call for participation from Canada, SoC Labs and Arm AAA will support you in developing your System on Chip projects, especially if you are an academic new to SoC and ASIC design.

The U15 Group of Canadian Research Universities

| Institution | Province | SoC Labs |

| University of Alberta | Alberta | Yes |

| University of British Columbia | British Columbia | Yes |

| University of Calgary | Alberta | Yes |

| Dalhousie University | Nova Scotia | |

| Université Laval | Quebec | |

| University of Manitoba | Manitoba | |

| McGill University | Quebec | |

| McMaster University | Ontario | Yes |

| Université de Montréal | Quebec | |

| University of Ottawa | Ontario | |

| Queen's University | Ontario | |

| University of Saskatchewan | Saskatchewan | |

| University of Toronto | Ontario | |

| University of Waterloo | Ontario | |

| University of Western Ontario | Ontario |

Canadian Universities, Higher Education Establishments and RTOs.

| Institution | Province | SoC Labs |

| Acadia University | Nova Scotia | |

| Algoma University | Ontario | |

| Algonquin College | Ontario | Yes |

| Carleton University | Ontario | Yes |

Project Milestones

Do you want to view information on how to complete the work stage ""

or update the work stage for this project?

-

Webinar, Make Academic System on Chip Projects Easy via Collaboration and Reusable Design.

Target DateCompleted DateHow the broad range of IP freely available via Arm Academic Access combined with academic-focused reusable reference designs and tape out flows are making System on Chip projects easier to undertake by individual students and larger academic teams. Examples of projects being developed by the SoC Labs academic community. A specific call for participation from Canada, SoC Labs and Arm AAA will support you in developing your System on Chip projects, especially if you are an academic new to SoC and ASIC design.

Result of WorkThe Webinar was delivered.

-

Workshop: Simplifying System-on-Chip (SoC) design and fabrication with Cadence workflow and ARM Reference Architecture

Target DateCompleted DateThe workshop will cover the complete SoC development lifecycle, looking not only at how to undertake an Arm based SoC design but providing help to simplify all the tasks associated with it. This includes how to maintain the EDA tool environment, how to utilise foundry PDKs for physical design leading to silicon validation of a design and how to work through all the steps successfully.

The workshop will use the SoC Labs freely available nanoSoC reference design, an Arm-based microcontroller SoC, and demonstrate how silicon-proven Cadence workflows and a GlobalFoundries technology node can be used to fabricate a design. nanoSoC has been taped out successfully with minimal cost and by individual Masters and PhD students. The workshop will also share some details of more ambitious SoC reference designs and highlight some custom accelerator integration examples for AI/ML workloads that can be used for more ambitious research projects.

Details are here

Result of WorkWe had over 265 registered for the workshop which was a great way to start 2026. Two more Canadian Universities have joined SoC Labs.

John Darlington

John Darlington

Add new comment

To post a comment on this article, please log in to your account. New users can create an account.