Interfacing with the Arm PL022 within a cocotb testbench

The Arm PL022 provides an interface for synchronous serial communication with peripheral devices connected to the SoC via the Advanced Peripheral Bus (APB). It supports a choice of interface operation, Motorola compatible Serial Peripheral Interface (SPI), National Semiconductor Microwire, or Texas Instruments synchronous serial interface. See the Techology page for details.

It uses an Initiator(or master) – Responder(slave) architecture, with the main device, usually a microcontroller, coordinating communication with a number of peripheral responder devices that are selected by chip select signal(s).

Typical use case include interfacing to various forms of memory and peripherals including Secure Digital cards, analog-to-digital (ADC) and digital-to-analog converters (DAC), sensors, etc.

The initial use case for SPI considered here will enable the use of off-chip storage mediums such as flash memory or a micro SD card. This will make it possible to copy code instructions into the SoC RAM.

Different SPI Configurations

Quad SPI (QSPI) adds additional I/O lines to exchange 4 data bits per clock cycle for faster data throughput. It adds an extra design constraint of 3 additional MIOSIO pins over the standard 4 wire SPI interface that a requires a responder select, clock , MISO and MOSI pins.

Current Plan of Action

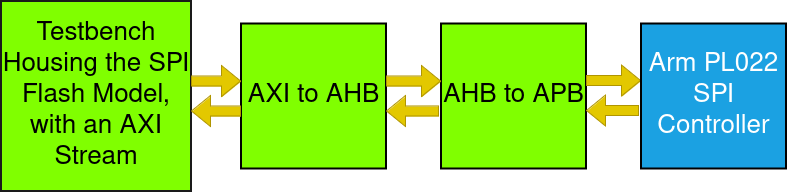

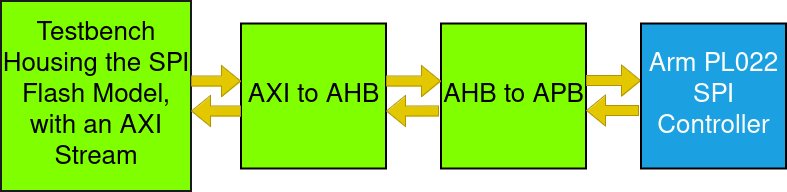

A cocotb test bench is being developed to ensure the correct configuration and operation of the following:

- (AXI->) AHB to APB Bridge

- Arm PL022 configured component "master"

- SPI flash device "model"

The python code will support the following:

- identify the attached serial flash device

- read/copy the contents of ROM to a file

- basic programming algorithm to re-program sectors of the Flash device

- file read-> program device demonstrator (small data for now)

- benchmark read bandwidth

The figure below illustrates a top level diagram of the proposed plan.

Current Progress

As of now, the cocotb test-bench and the makefile, responsible for integrating the test-bench with the Arm PL022 verilog files together, are under development.

PL022 SPI - Synchronous Serial Port

PL022 SPI - Synchronous Serial Port

Comments

Source code repository link

Hi,

Is there a link we can add for the source code?

Add new comment

To post a comment on this article, please log in to your account. New users can create an account.