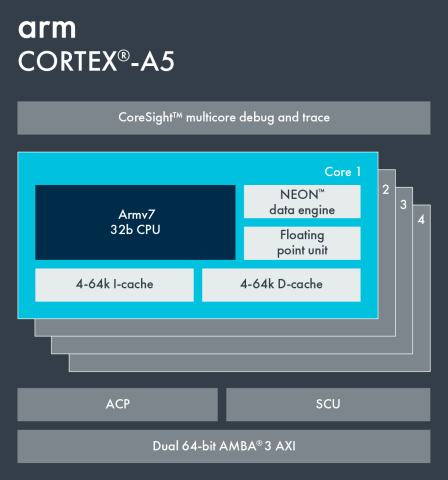

Cortex-A5 (UP and MP)

The Cortex-A5 processor (UP uniprocessor or MP multiprocessor) has an 8-stage in-order pipeline with dynamic branch prediction, 32 bit physical addressing, Level 1 cache, 64-bit AXI master interface and optionally either a Floating-Point Unit or a NEON Media Processing Engine. Level 2 cache can be added to a SoC with an external Cache Controller such as the PrimeCell PL310.

The Cortex-A5 processor implements the ARMv7 architecture, the TrustZone security extensions and runs 32-bit ARM instructions, 16-bit and 32-bit Thumb instructions, and 8-bit Java bytecodes in Jazelle state. It supports two power domains, one for the CPU and one for memory.

The Snoop Control Unit (SCU) connects between one and four processor cores to the memory system maintaining data cache coherency and arbitrating access for any Level 2 cache access. The Accelerator Coherency Port (ACP) is an AXI 64-bit slave port which can be connected to a DMA engine or a non-cached coherent master.

Explore This Technology

Add new comment

To post a comment on this article, please log in to your account. New users can create an account.