megasoc re-usable SoC platform

Rationale

megasoc has been designed to provide a complex SoC component that can 'host' and support the development and evaluation of research components or subsystems. The design allows for seamless transition from FPGA to physical silicon implementation via a pre-verified programmable control system that allows reuse of software and diagnostic functionality to facilitate the configuration, control and diagnostic analysis of research hardware such as custom accelerators or signal processing.

The design is based on an Arm Cortex-A53 CPU core with inspiration from the Corestone 1000 subsystem from Arm. megasoc allows the reuse of the AAA pre-verified IP, documentation and software but it is architected to support simple 'bolting-on' of experimental hardware. The aim of megasoc is to provide a fully Linux capable SoC whilst minimising the cost of physical silicon production.

Technical Overview

megasoc is a complex SoC utilising the Cortex-A53 processor with pad-level support for silicon implementaation. Included is:

- CPU - Armv8-a Cortex A53 processor

- Interrupt Controller - GIC 400

- Software Debugger - Arm DAP-lite

- Boot ROM

- XiP QSPI - For program or BIOS

- SRAM

- NIC 400 System Bud

- DRAM controller

- DMA for system support - Off-chip mem to DRAM

- Peripherals (UART, Timers, etc)

Architecture

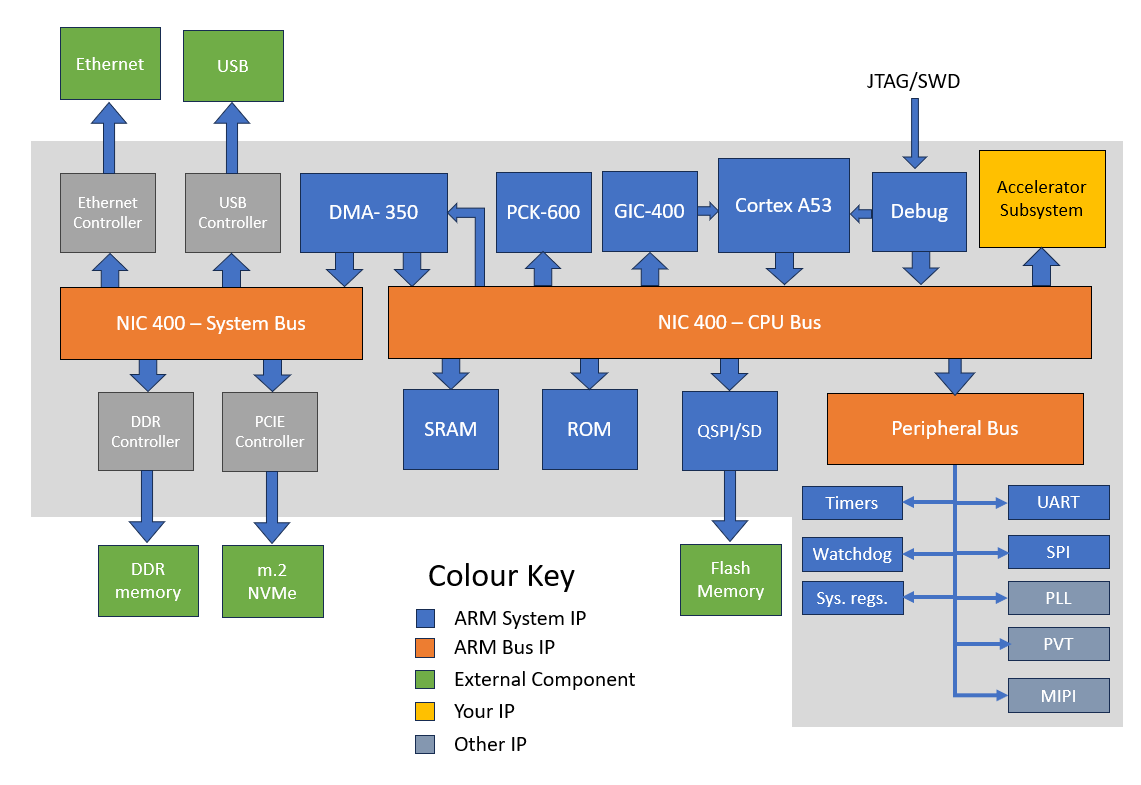

The overall architecture is as shown below. This has been seperated into 2 main sections, the CPU and System sections. Development so far has been focused on the CPU subsystem, as we are currently exploring options for sourcing the IP for the ethernet, USB, DDR and PCIe controllers.

Address Map

The Cortex A53 has a 40-bit address interface, this gives a total addressable space of 1 TB. For now a simplified 32 bit address map is being created, it is likely that any higher address will be used to expand the DRAM and possibly for direct access from the CPU to the communication interfaces (PCIe, USB, Ethernet) if possible, although these will all likely be controlled by DMA transfers.

Currently this address map is unoptimised (some regions are much larger than neccessary, and there are a few empty regions which will likely be filled as development progresses.

| Start Address | End Address | Region | Size |

|---|---|---|---|

| 0x00000000 | 0x0000FFFF | Boot Rom | 64 KiB |

| 0x00400000 | 0x007FFFFF | QSPI Flash | 4 MB |

| 0x00800000 | 0x0080FFFF | SRAM | 64 KiB |

| 0x01000000 | 0x0100FFFF | Flash and Cache Control | 64 KiB |

| 0x01010000 | 0x01011FFF | DMA Control | 8 KiB |

| 0x01100000 | 0x01107FFF | GIT 400 Control | 32 KiB |

| 0x40000000 | 0x5FFFFFFF | Peripheral | 512 KiB |

| 0x60000000 | 0x7FFFFFFF | Debug | 512 KiB |

| 0x80000000 | 0xFFFFFFFF | DRAM | 2 GB |

CPU Interrupts

The GIC-400 generic interrupt controller supports a maximum of

| IRQ Number | Source |

|---|---|

| 32 | DMA350 Channel 0 interrupt |

| 33 | DMA350 Channel 1 interrupt |

| 34 | DMA350 Channel 2 interrupt |

| 35 | DMA350 Channel 3 interrupt |

| 36 | DMA350 common interrupt |

| 37 | UART0 Transmit interrupt |

| 38 | UART0 Recieve interrupt |

| 39 | UART0 TX Overrun interrupt |

| 40 | UART0 RX Overrun interrupt |

| 41 | UART0 Combined interrupt |

| 42 | TIMER0 interrupt |

Communication channel

Currently implemented is a single UART channel for off-chip communications.

Pinlist

| Pin/Port | Function |

|---|---|

| REF_CLK_XTAL1/2 | Main System clock from crystal oscillator |

| RT_CLK_XTAL1/2 | Real time clock input from crystal oscillator |

| PORESTn | Active low power-on-reset |

| nSRST | Active low System reset |

| GPIO_P0[15:0] | GPIO Port 0 |

| GPIO_P1[15:0] | GPIO Port 1 |

| QSPI_SCLK | Clock output from QSPI controller |

| QSPI_nCS | Chip select output from QSPI controller |

| QSPI_IO | Data I/O from QSPI controller |

| FT_CLK | FT1248 Clock |

| FT_SSN | FT1248 Chip Select |

| FT_MISO | FT1248 input |

| FT_MIOSIO | FT1248 IO |

Using megaSoC

If you'd like to use megasoc for your custom hardware, you can fork or clone the megasoc project git repository. This SoC reference design is still under development, expand the V1 Tapeout section below for more details.

megaSoC V1 Tapeout

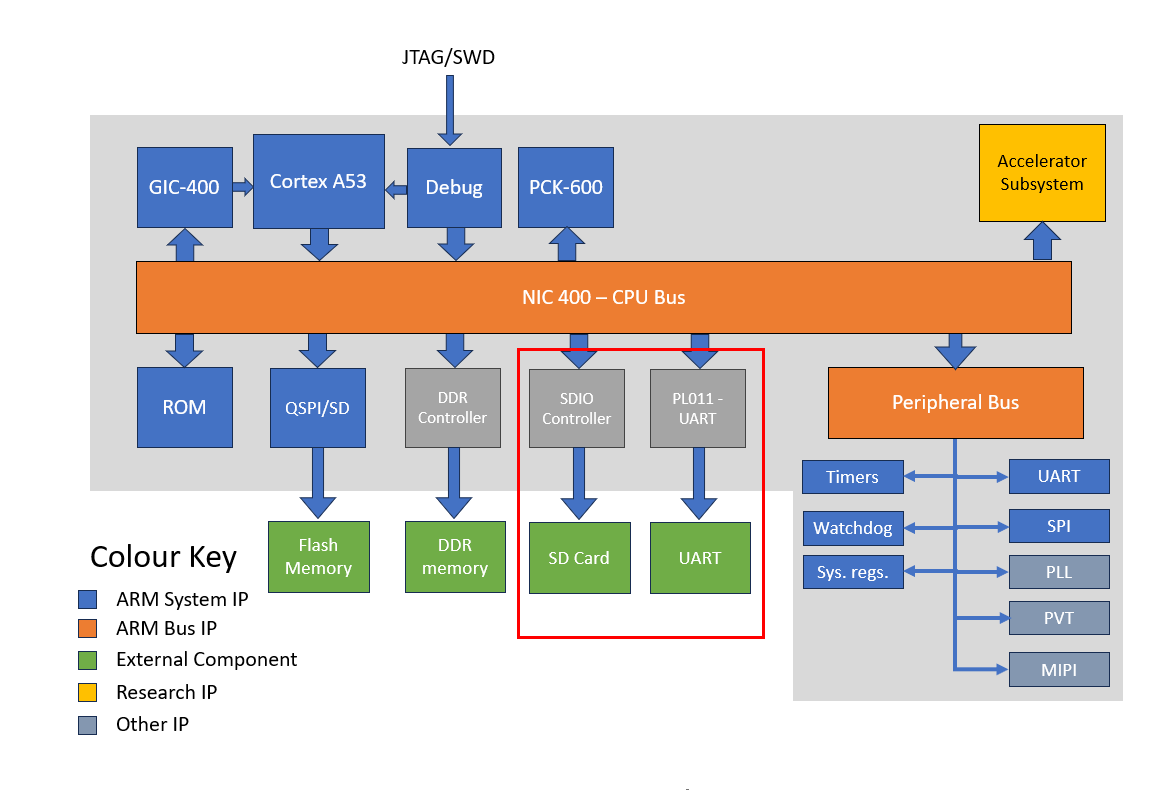

- megaSoC V1 - Architectural Changes

Work is currently underway to tapeout megaSoC in 2026. This initial version will be a "Minimal Viable Product" version of megaSoC. This version will not have the complexity of high speed external interfaces and the PCIe, USB and Ethernet subsystems.

The aim for the initial tapeout of megaSoC is to prove the core compute system, the fabrication flows and provide a good baseline of information to the community on taping out an A-class processor on an advanced technology node. As with the first version of nanoSoC some application scenarios may be limited it will serve as a good foundation for future improvements.

These two controllers will be replaced with an SDIO controller (ZipCPU SDIO) and a UART controller (PL011 from ARM)

Network over UART

Whilst not ideal, networking is possible over UART. And this is the plan for the MVP implementation of this megaSoC-lite version. Network communication is possible using packages like PPP in linux (an example on how to set this up between 2 raspberry pi's). The PL011 from Arm has been chosen as it allows for hardware flow control which is ideal for this application.

SD card filesystem

Ideally a very high speed non-volatile memory would be used for the filesystem using a PCIe interface to integrate an M.2 SSD device. However, it is quite common practice to use SD cards for such applications. The implementation of a PCIe interface and associated PHY for the SD controller is the target for a later version. The ZipCPU project is mostly focused around FPGA implementations and so whilst there is a lot of information available it would require a custom PHY implementation. Without a PHY the system would be limited in the bandwidth achievable for the SD card.

DDR Controller + PHY

For this project, Synopsys have kindly donated their DDR controller and PHY IP to soclabs. The specific parts used in this project are the uMCTL2 DDR controller and LPDDR4 multiPHY. This will allow for an implementation of megaSoC as a single board computer (SBC), with LPDDR4 module on the PCB. For this initial prototype of the project we are keeping this as simple as possible, and so using a 16 channel LPDDR4 device (most likely something like the D1611PM3BDGVIW-U device from Kingston technology).

For this configuration we are using a 16 Gbit (2GB) device, which we believe will give us a good starting point to ensure enough memory for the OS performance, whilst keeping complexity and cost to a minimum.

- Backend - Hierarchical design Planning

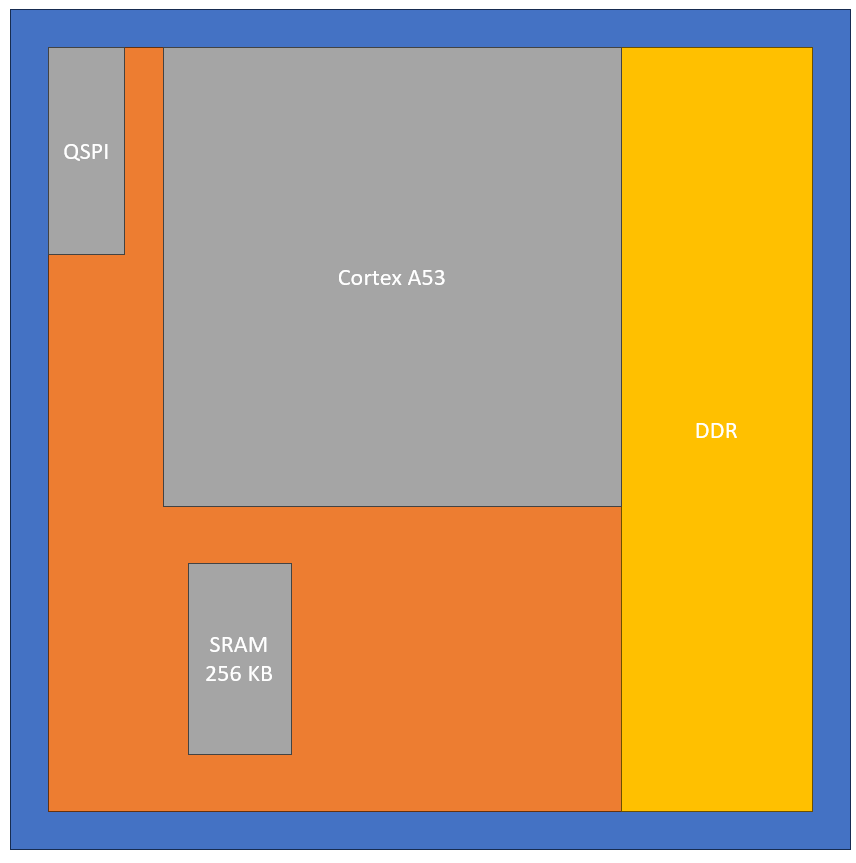

As the megaSoC design is a large SoC, the backend work must be done in a hierarchical/bottom up approach. This means dividing the design into sublocks, performing backend on each of those blocks and then bringing the whole design together.

Synopsys Fusion compiler includes a flow for hierarchical design planning that also allows you to break the design into blocks but run the backend in parallel for each of those sub-blocks. This ensures all blocks are in sync at each of the design steps and you can run verification after each point (e.g. post clock opt gate simulations/logical equivalence)

Floorplan

It is a good idea to have initial floorplan of how the blocks will be split up. Below is an initial estimate for what the floorplan will look like. We expect the A53, DDR, SRAM and QSPI controllers to be the largest IPs that should be worked on hierarchicaly. The NIC400 bus to also expected to be fairly large, but may be best for this to get merged into the top hierarchy as it will likely be distributed across the entire chip.

In terms of IO. We are expecting that the die will be about 2.2 x 2.2 mm, using a bump pitch of 200um this means we can have a total of 121 IOs (linearly arranged). The number of IOs is as follows:

- Clocks + resets - 3

- SWD/JTAG - 6

- QSPI - 6

- GPIO - 32

- UART (RS232) - 10

- LPDDR4 - 39

- SDIO - 7

This gives a total of 103 for the signal pins. Leaving 18 bumps for power and ground, ~ 4 per side (VDD, VSS, VSSIO, VDDIO).

Using the equations from the datasheet given with the GPIO libraries, we can calculate based on the number of GPIO's used, that we need 16 VDDIO/VSSIO cells. So we need to revisit the total number of bumps to accomodate the power supply pins needed.

For now we are going to assume that the die size stays the same, but we will reduce the bump pitch to 150 um. This would give us a total of 196 IOs. With 103 signal bumps, it leaves us with 93 power/ground bumps. This would give a maximum of about 23 per side (5-6 of each VDD, VSS, VSSIO and VDDIO). This now may be overkill, but in reality what we will probably do is reduce the density of bumps at the center of the die (to improve routibality on the final package).

Hierarchical Design Planning

To perform hierarchical design planning, you need to at least run initial synthesis for the blocks as the tools expect a netlist rather than behavioural HDL. Steps are as below

- Synthesise blocks to netlists

- Import netlists as verilog outlines in fusion compiler (read_verilog_outline command)

- Initialise Design

- Place I/Os

- Explore Hierarchy and commit blocks

- Create placement abstracts

Project Milestones

Do you want to view information on how to complete the work stage ""

or update the work stage for this project?

-

Tape Out

Design FlowInitial (ambitious) deadline for tapeout on europractise MPW for TSMC 16nm

-

Architectural Design

Design FlowTarget DateCompleted DateOverall architecture of megaSoC

Result of WorkThe overall architecture is complete for this and can see from the architectural diagram.

-

Getting Started

Design FlowCompleted DateResult of WorkEnvironment already setup for this project in the SoCLabs server

-

Specifying a SoC

Design FlowCompleted DateResult of WorkThe aims for the SoC is to build a linux capable system. This will be achieved using an application class processor (A53) with filesystem storage (SD card), and system memory (LPDDR4). The networking for this initial version of the SoC will be performed using SLIP (serial line internet protocol) over UART.

-

IP Selection

Design FlowCompleted DateResult of WorkThe SoC consists of:

- Arm Cortex A53

- Arm GIC-400

- Arm PCK-600

- Arm NIC-400

- SoCLabs QSPI AHB controller

- Arm Corstone 101

- Arm PL011

- Open source SDIO controller (from ZipCPU)

- Synopsys uMCTL2 DDR controller and LPDDR4 multiPHY

-

Behavioural Design

Design FlowTarget DateMost of the SoC is complete and simulated. However work is ongoing particularly on the reset controller, clock controller and DDR controller

-

RTL Verification

Design FlowTarget DateVerification of the system is ongoing. Most of the subsystems/IP are pre-verified. So only integration verification is needed. Parts still to be verified are:

- DDR controller

- SDIO controller

- Reset controller

-

Technology Selection

Design FlowCompleted DateResult of WorkAim for this project is to tape out with Europractise on the TSMC 16nm MPW

-

Synthesis

Design FlowTarget DateInitial synthesis of the Cortex A53 is near completion.

The rest of the SoC is still to go. The plan for this is to do a hierarchical approach, so the Cortex A53 and DRAM controller will be synthesised seperately, then integrated into the full system.

-

Design for Test

Design FlowTarget DateIn this complex SoC we have yet to decide exactly what scheme we will use for DFT.

This is a point that needs further clarification/discussion in the team

-

Logical verification

Design FlowTarget DateLogical equivalence checking and gate level simulations will be needed.

For a SoC of this size, gate level simulations may be impractical, but are usually good to check bootup sequence at the very least

-

Floor Planning

Design FlowTarget DateAs we are planning on using Synopsys Fusion Compiler for the backend, floorplanning and synthesis will happen simultaneously.

The hierarchical approach will mean treating the Cortex A53 and DDR controller as macro blocks.

Some time will be allocated for floorplan exploration as well

-

Clock Tree Synthesis

Design FlowTarget Date -

Routing

Design FlowTarget Date -

Physical Verification

Design FlowTarget DateFull DRC, STA, and LEC should be complete on this design.

Initial DRC will be complete before 30th June 2026, as that is when we have to register for the tapeout slot. Ideally at this point we will have some idea on how realistic an october tapeout will be

Daniel Newbrook

Daniel Newbrook

Cortex-A53

Cortex-A53 CoreLink NIC-400

CoreLink NIC-400 Corelink DMA-350

Corelink DMA-350 PCK-600 Power Control Kit

PCK-600 Power Control Kit GIC-400 General Interrupt Controller

GIC-400 General Interrupt Controller

Add new comment

To post a comment on this article, please log in to your account. New users can create an account.