Interference Detection and Mitigation Accelerator for Automotive Radar SoCs

Advancements in electronics, wireless communications, and sensing technologies have made possible a multitude of smart sensing features in automotives. Integrating high-frequency sensors, digital signal processors and hardware accelerator engines on a single system on a chip (SoC) enhances sensing computation potential of radar sensors utilized in automotives. However, as the number of vehicles equipped with such wireless SoC sensors increases so does the likelihood of mutual wireless interference among these sensors leading to performance degradation and compromising safety of such systems.

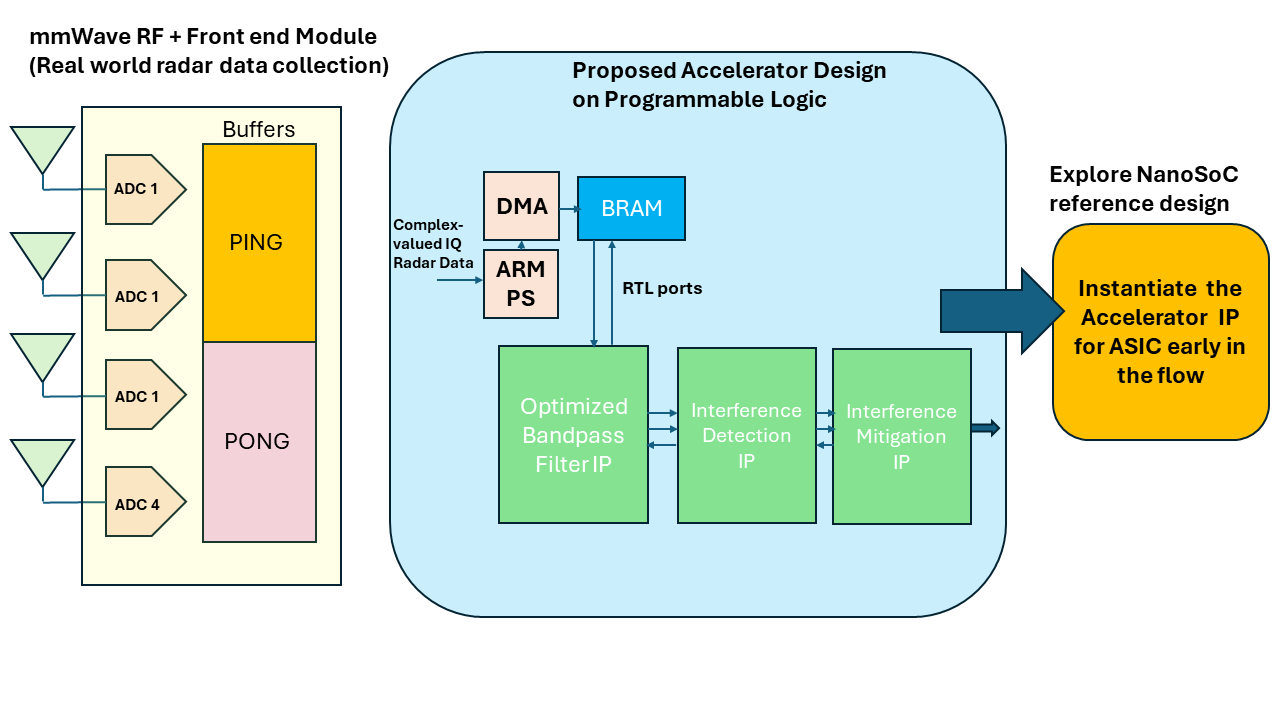

The main aim of the project is to design advanced digital signal processing modules for wireless radar sensor SoCs which can detect and mitigate mutual interference. High level system model of the proposed project showing various modules is presented in the above figure. Our interference-awareness and mitigation design will allow the use of interference mitigation module on an as-needed basis in the SoC. This means that interference mitigation processing chain will only be enabled when required which has the potential to enable power savings in the SoC.

Project Milestones

Do you want to view information on how to complete the work stage ""

or update the work stage for this project?

-

Architectural Design

Design FlowTarget DateArchitectural Design of Accelerator Modules

-

Milestone #2

Target DateModelling/Simulation

-

Milestone #3

Target DateAccelerator Design Implementation

-

Generate RTL

Design FlowTarget DateMilestone 4: RTL generation using Xilinx Tool

-

RTL Verification

Design FlowTarget DateVerification using Xilinx Tool

-

Milestone #6

Target DateFPGA flows

-

Milestone #7

Target DateNanoSoC reference design exploration

-

Physical Design

Design FlowTarget DateDeveloping ASIC (65 nm) flow and integration possibility of accelerator with nanosoc

-

NA

Target Date -

NA

Target Date -

NA

Target Date -

NA

Target Date -

NA

Target Date

Comments

Progress on Milestones

Hi,

I hope you had a good summer break. How are things progressing on the project milestones?

We look forward to hearing from you.

Data bandwidth requirements

Hi,

Do you know the data throughput requirements you are expecting for this application.

If you can let us know that may help define the SoC system.

John.

Data bandwidth requirements

Our data throughput is 50 Mega samples per second. Currently we are processing data from two receive antennas. For more antenna receive one can scale it up easily to realize what is the throughput need. We dont expect to process more than 1-2 receive antennas so 50 mega should be good to go.

Thanks

Zaheer

Milestone 1: Architectural Design

Hi,

How are you getting along with the initial milestone?

John.

Milestone 1: Architectural Design

Hi, Thank you for your question and sorry for late response.

Yes, for the proposed accelerator architectural design is fine.

One question:

From Oulu University side it seems that we are not part of Arm AAA program.

Do you think this to be a bottleneck for this project?

There is a AAA form which someone from our University side can fill and submit but it seems that there is also a legal contact require. This might have some legal paperwork bureaucracy which I am not sure if our University may want to participate in.

Other question is that your soclabs website mentioned about obfuscated ARM IP usage which seems to be a possible way.

Do you think it is good enough to follow this path and run the given accelerator project at SoCLabs / Accelerator Project · GitLab (soton.ac.uk)

as when we try to run socsim simulate/socsim/test_aes128.sh TESTNAME=aes128_tests it asks about ARM IP

Arm AAA program agreement

Hi,

There are already over 100 universities that have signed up to the standard agreement and we have along the way revised the agreement a few times to make sure it is easily adopted. Your University should not have any concerns that have not already been addressed. Please connect me to any contracts person if needed. It should be a simple process to get this in place.

You will need a bit of help to set up the license server access, Lance wrote an article on creating the environment for Arm Academic Access we have at Southampton.

You may be able to make some progress with the obfuscated ARM IP for the M0.

Simulating Nanosoc

Hi Zaheer,

After our call today on how to simulate nanosoc. The problem is entirely my fault, I made changes in the repository and forgot to update the documentation. The command to use socsim has changed as I removed the reference to system_aes128 as this was one of the example projects (AES 128 encryption project)

If you want to run the simulations using socsim the command should be:

socsim test_nanosoc TESTNAME=hello

which will run the hello world test. There are a few different tests that you can run, you can find the name for these in the nanosoc_tech/testcodes directory.

Currently socim will run a QuestaSim (mti) simulation, if you want to use a different simulator then you can also cd into nanosoc_tech and run make run_mti, run_vcs or run_xm for Questasim, Synopsys VCS or Cadence Xcelium.

I'll update the documentation in the repository shortly

Add a link to the repository

Daniel,

Can you add a link here to the code repository? That will make it easier for people.

John.

Repository link

Hi John,

Yeah of course. The link to the nanoSoC accelerator project repository is here https://git.soton.ac.uk/soclabs/accelerator-project

Daniel

Analog front-end

Hi Zaheer,

This looks like a very interesting project. I wonder if you might be able to add a bit more detail on what the front end of this looks like?

I'm just wondering what kind of signals you are recieving, are these modulated (and in need of demodulation) or is the aim to have high speed ADC's that can work in GHz range?

Analog Front end

Thank you for showing interest. Our proposed SoC system processes complex baseband mmWave radar IQ samples.

Our design works in purely digital domain on FPGA-SoC (PL with ARM PS). Our interest is of course to be able to integrate

our logic part of the design (accelerator) via some wrapper to your SoC flow.

Please note that constructing mmWave analog front end is serious amount of extra and non-novel work which does not suits the University research needs.

For testing the system we use real Radar IQ data captured using TI radar chip and communicated via ethernet or USB or some other port.

I hope this clarifies and answers your question.

Add new comment

To post a comment on this article, please log in to your account. New users can create an account.