ASIC for parallel channel tuning on Reconfigurable Intelligent Surfaces

Reconfigurable Intelligent Surfaces (RIS) are planar structures composed of large arrays of tunable elements that can dynamically redirect, reflect, or shape wireless signals in the environment. As wireless communication standards evolve toward ultra-high throughput, ultra-low latency, and massive connectivity, RIS offer a promising low-cost and energy-efficient alternative to traditional active phased arrays or beamformers for enhancing spectral efficiency, signal coverage, and network energy performance, which has been poised as one of the major technology breakthroughs in future wireless networks.

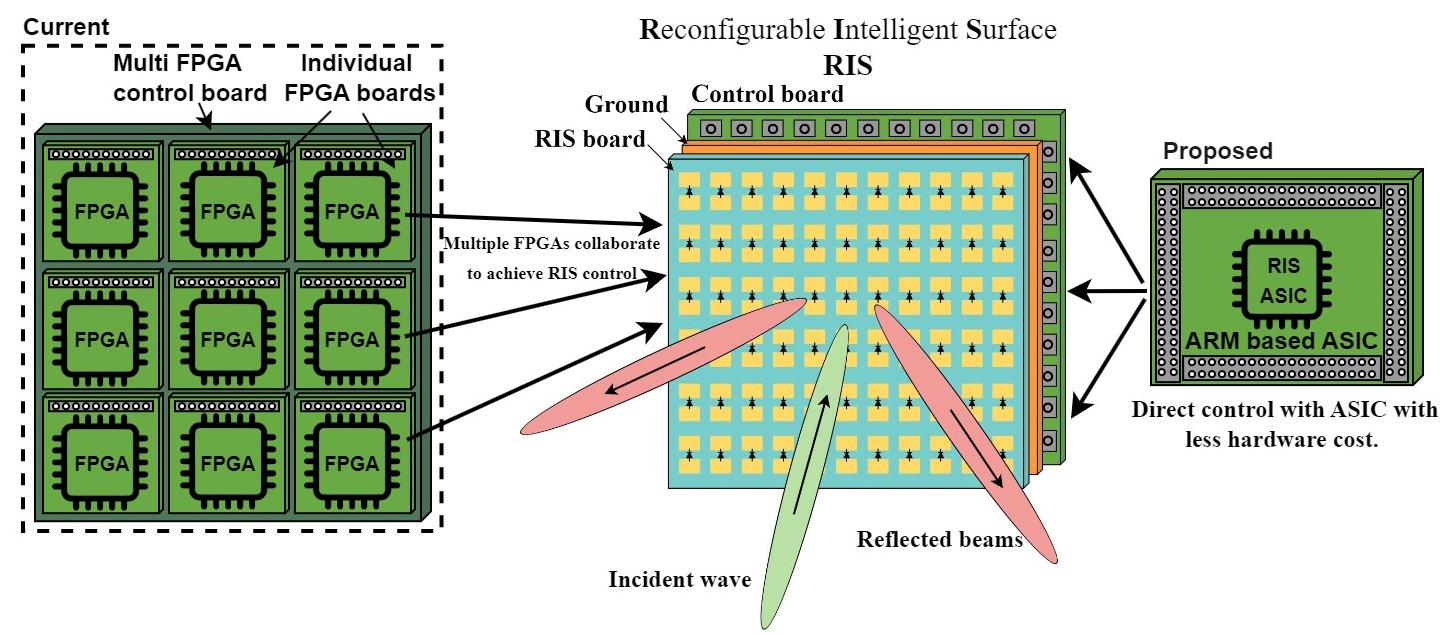

The complex beamforming functions on RIS rely on the dynamic tuning of voltage-controlled diodes, varactors or tunable materials on individual unit cells. The control system must support fast, synchronised tuning over hundreds to thousands of control channels. In current implementations, large-scale RIS control often relies on multiple FPGAs working in parallel to overcome the limited number of I/O pins. This approach results in high power consumption, increased system complexity, and elevated hardware costs, creating significant barriers to scalable and practical RIS deployment.

This project aims to develop a dedicated ASIC for RIS control, addressing the key limitations of FPGA drivers. The ASIC targets the following key design objectives:

- Low Power Consumption by leveraging mature low-power ARM Cortex-M0/M0+ cores.

- High I/O Scalability: Supporting up to 512 digital output channels to meet the drive requirements of large-scale elements tuning.

- Cost Efficiency: Utilising mature IP designs and CMOS nodes to reduce the overall design and manufacturing costs.

- Scalability and Configurability: Flexible configurations for memory and I/O interfaces, enabling the ASIC to support a wide range of RIS sizes and functionalities.

The development of a dedicated RIS ASIC aims to provide a standardised, low-cost, and power-efficient control platform for RIS in both academic research and industrial applications. In the early phases, the project will actively engage with the RIS research community to gather requirements and explore opportunities for co-development. The initiative also plans to release development kits or a semi-open ASIC design framework to encourage further innovation and collaboration. This method has the potential to promote interdisciplinary collaboration among experts in RF engineering, embedded systems, and wireless communication, aligning with the broader vision of scalable, intelligent, and energy-efficient future wireless networks.

Project Milestones

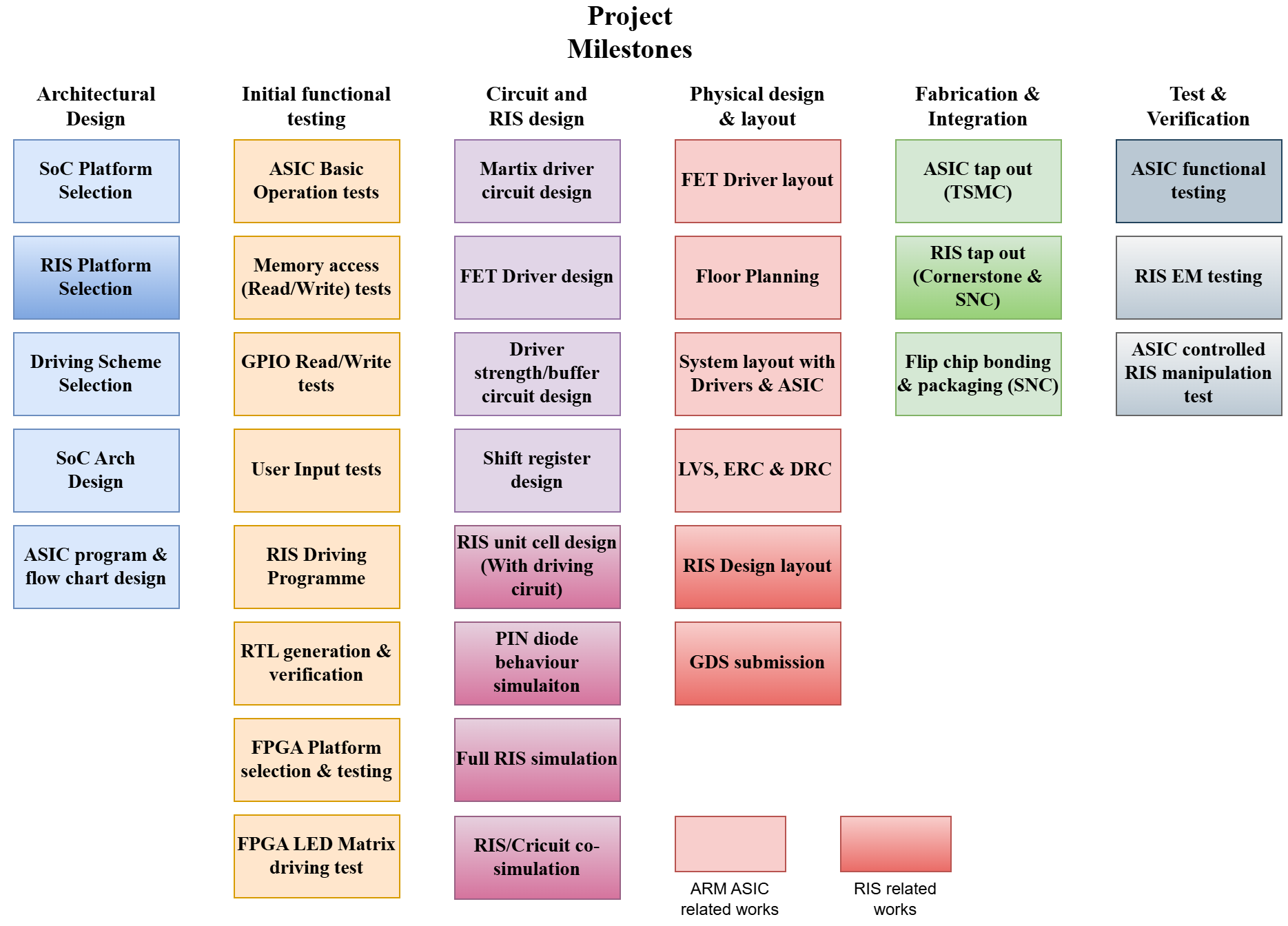

Figure 2: Project milestones of the project contain 6 major design & verification phases.

Architectural design: Initial design of the SoC platform, driving scheme and control scheme over the RIS.

Initial functional testing: Design and verification based on the nanosoc - baseline Cortex-M0 microcontroller, with verification over the required memory access, signal driving capabilities for the RIS.

Circuit and RIS design: Circuit design and simulation take place in this phase, which involves the matrix driver, FET driver, buffer drivers and shifter register units to meet the current and driving patterns required by the RIS. RIS is required to co-design with the driving patterns from the microcontroller.

Physical design and layout: This stage involves the physical layer design and layout of the circuit and RIS before final tape out. The ARM microcontroller and RIS will be fabricated on separate microfabrication platforms and integrated via flip-chip bonding.

Test & Verification: Test and evaluation post-fabrications on the RIS and microcontroller.

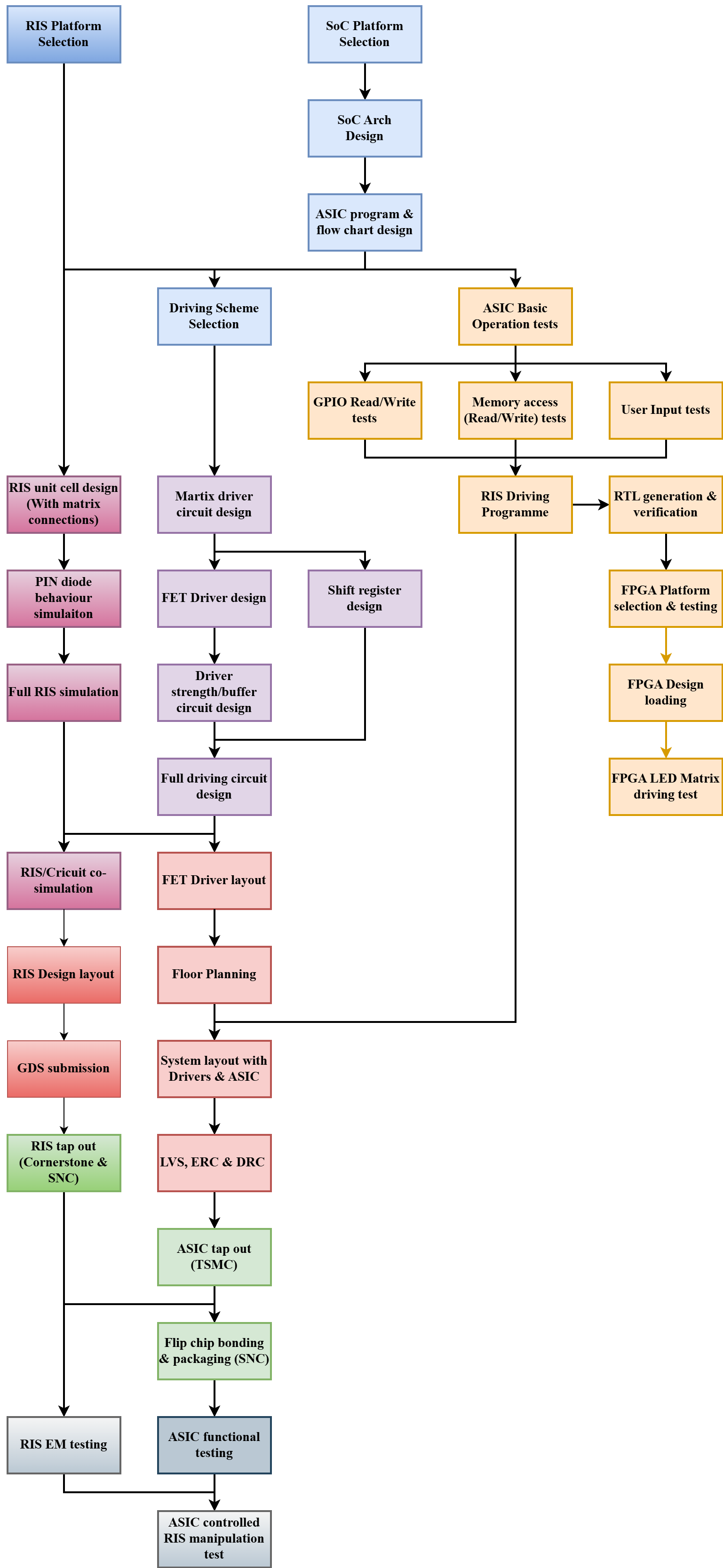

Planned project flow based on Milestones

Project Milestones

Do you want to view information on how to complete the work stage ""

or update the work stage for this project?

-

Getting Started

Design FlowTarget Date13th April 2026: Added specific milestone plan for the project.

Zhicheng Shen

Zhicheng Shen

Cortex-M0

Cortex-M0

Comments

GPIO Drive strength contoller

Hi,

One thing to think about, the current GPIO controller in nanoSoC doesn't have any way to control the drive strength of the pads. This could be a useful thing for your system, so that if you need to make any fine tuning/adjustment to the output current of the drivers. On the physical side it would be something like this:

And the digital side would need a few bits to control the drive strength of each pin (or you could control all of them with a single value)

First draft.

First draft.

Getting Started

Hi,

Great to see this project in SoC Labs. I think the first thing to do is look at the Getting Started milestone so that we can make sure you have access to all the right tools and IP as well as helping structure the project. Happy to have a Teams call to discuss anything.

First thing click on the Getting Started milestone, view the information and then update your first milestone.

You may want to look at Sydney's example project as they have some great Milestones as examples of how to add them.

Sensing for Precision Agriculture | SoC Labs

Look forward to hearing from you,

John.

Getting Started

Hi,

We need to make sure you have access to AAA IP and also the EDA tool flows and also any Git repo, etc. It would be good if we can confirm everything is in place in terms of 'Getting Started'.

John.

Update to Milestones

Hi,

Do you have any progress that we can add to the Milestones for the project?

John.

Add new comment

To post a comment on this article, please log in to your account. New users can create an account.