SoC Design Contest 2026 for Canada and the America's

In association with CMC Microsystems and Arm we are extending our design contest specifically supporting institutions from Canada and the America's with support for their projects, conference attendance and financial help with silicon tape out.

People wishing to take part can look at prior contests and projects such as those for our now closed SoC Design Contest 2024/25: Understanding Our World.

The contest will again support two alternate tracks:

Collaboration/Education track focuses on developing SoC design skills within the academic community and broadening the range of institutions undertaking SoC design activity. The focus is not on the specifics of the hardware design, although the technical requirement is similar to the Hardware track below. The focus is on how teams develop community collaborations and clearly show institutional and individual skill development in SoC design. It does no require a unique hardware concept. Teams can reuse design from other groups either for a new application or simply as a skills development activity; perhaps forming a collaboration to re-purpose open-source IP into community re-usable IP working with others in the institution or across institutions.

Groups interested in working with other prospective collaborators should post details of their Arm-based project idea to SoC Labs, including enough detail of progress to date to help others engage. SoC Labs will try and help with the formation of shared community hardware projects. Alternatively, academics involved in teaching SoC design may submit a project summary detailing their approach, including benefit for the community.

Hardware Implementation track focuses on innovative design for a) a mixed signal SoC containing both analogue front end and digital components or b) a SoC that clearly demonstrates how compute (including custom acceleration) makes use of real world data to show clear impact. There is no prescribed analog / digital bias, custom compute / traditional analog is acceptable.

A mixed signal design can address one or more of the many areas of interest in mixed signal systems, calibration, accuracy/sensitivity, noise, energy efficiency, novel compute, and many more. The analogue and digital parts have different design characteristics and their efficient integration into a mixed signal SoC design would be a focus. A design focused on compute will highlight the use of data about the external environment within the SoC and processes by which signals converted from analogue real world events are used to compute outcomes that can be effectively operated on in the real world. There is obviously great interest in applications of machine learning and Artificial Intelligence supported by custom acceleration hardware.

The application area is open and could range from a simple novel sensor with a single signal to a more complex pixel-based sensor platform requiring highly parallel signal processing. Data from a simple vibration using a simple microcontroller to video data using a complex linux capable system.

Eligibility Criteria:

The contest is open to universities or research institutes based in Canada and the America's but can have partners in other geographies. Only Arm processor-based designs will be considered. The Arm Academic Access (AAA) program is open and ready to receive applications from universities and research institutes to provide access a suite of Arm IP to empower your work on Arm. The contest is open to research groups with members working within a university/research institution or individual academics involved in SoC Design teaching. Research groups applications can also be from postgraduate students, but applications from postgrads should be supported by a senior member of staff in the same institute who is supervising them. Multiple applications from the same institution can be submitted and supervisors can support more than one postgrad student.

Entry submission and applying:

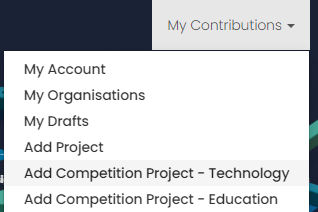

Entry is via this site. You will need to sign up to SoC Labs as described on the home page.

When you are logged in, a Project summary should be submitted via the ‘My Contributions’ tab and dropdown at the top right. You need to use the ‘Add Competition Project’ action.

A project has a timeframe and uses the two other significant aspects of a SoC development, the selection of technology or IP blocks that make up the SoC and the design flow that is followed from specification through to final instantiation of the system. We have a growing number of example flows using both industry EDA tools and open-source alternatives. To make things easy for people to engage with the contest we have created reference SoC designs, eg. NanoSoC and an example competition design flow to follow.

Alternatively: Collaboration/Education tracks can use this link to create an entry; Hardware Implementation tracks can use this link to create an entry.

Submissions take the form of a project summary of no more than 350 words, written in English. For those interested in the Collaboration/Education track you should consider providing a set of milestones that help show how your SoC design skills development project will be demonstrated.

Important Dates:

Competition opens: OPEN

Further judging announcements to determine a place on the target sponsored shuttle: Deadline TBC.

Rewards/ Prizes:

Where rewards or prizes are given, they will be for the best project(s) in each track, as determined by the organizers. Rewards including invites and subsidies for travel to conferences and costs associated with silicon tape out of projects designs.

Judging:

The judging criteria will centre on how effectively (a) teams achieve self-defined goals and (b) the extent to which the journey has the potential to assist other research groups around the world to push research and development boundaries. The contest theme is open to all manner of research topics, without prescription.

In terms of the relative balance of judging criteria, the focus is on shared improvement in line with our aims, the distribution will be as follows:

Project Progression (40%): Overall management of the project. Commitment to providing regular community updates to SoC Labs that help draw others in (these may include both progress and setbacks/calls for help using various communication channels).

Reusability and impact (40%): the potential to assist other research groups around the world to push research and development boundaries. Especially verification efforts where academic activity is less well developed. And that promote broader collaboration with other disciplines, physicists, chemists, mechanical engineers, clinicians, etc.

Technical complexity (20%): for the type of track and quality of implementation .

The judging panel will be geographically balanced and will include judges with specific interest in the three key aspects, community, reusability and technical complexity.

IP statement:

Teams are encouraged to share their designs where relevant. The default position is that third parties should be able to recreate the outcomes of any projects submitted to the competition. If there is some aspect of your design that is sensitive, you may submit details of the method rather than the IP block details itself. Any IP statements and conditions of use should be made clear.

More details:

We will be posting some additional details here and responding to any frequently asked questions. You are welcome to add any questions by using the comment field below.

John Darlington

John Darlington

Add new comment

To post a comment on this article, please log in to your account. New users can create an account.