System Verification of NanoSoC

Performing system-level verification on a System-on-Chip (SoC) design is crucial for ensuring the correct function and overall performance of the entire system, rather than individual components. This project is aimed at developing the necessary resources and design flow stages for the verification of the NanoSoC reference design.

Architectural Design: Verification Methodology

With NanoSoC, there are multiple options for performing system-level verification.

One verification framework being developed in this Project uses a Python co-simulation environment called Cocotb. Cocotb was chosen for 1) quick creation of a verification environment, 2) the growing use of Python as a language in the verification and design community and 3) support for the use of multiple simulators. Cocotb supports drive and monitoring of an RTL test bench, and with bus extensions allows generation of stimulus and checks against references in a single script. The other advantage of this approach is the ability to reuse test components for testing at chip-level, on FPGA designs and within ASIC testbeds.

System-level verification involves testing the integrated SoC with all its components, subsystems, and external interfaces, emulating the real-world operating conditions and use cases. Some of the important things to test for at a system level are:

- Integration Validation - have components been connected into the system correctly.

- Interaction Verification - are components able to communicate with one another.

- Use-case validation - are the intended use cases of the system able to be carried out correctly.

- Performance validation - is the system able to meet performance requirements, especially in required use cases.

- External Interface Verification - how does the SoC interact with the outside world and are use cases tested.

Within the constraints of this system testbench, a Verification Plan can be generated for NanoSoC. This aspect of the Project is currently being worked on but the sections are:

- Laying out the objectives of the VPlan

- Specifying the scope of the testing - which features and components are to be tested and which are we not

- Specifying test environment - which tools, simulators and coverage analysers are being used

- Set out Verification goals - aims to hit on functional and code coverage of design

- Create a list of feature points to create tests against

- Generate a list of tests to get complete feature coverage

As the project is progressed and completed, the testbench for the NanoSoC will be created and confirmed in actual testing phase against the NanoSoC. More to follow...

Behavioural Design: RTL verification

NanoSoC is a basic SoC framework comprised of an Arm Cortex-M0, Arm DMAC, a SoCLabs SoCDebug debug manager and a variety of subordinate regions containing accelerators, peripherals and memories.

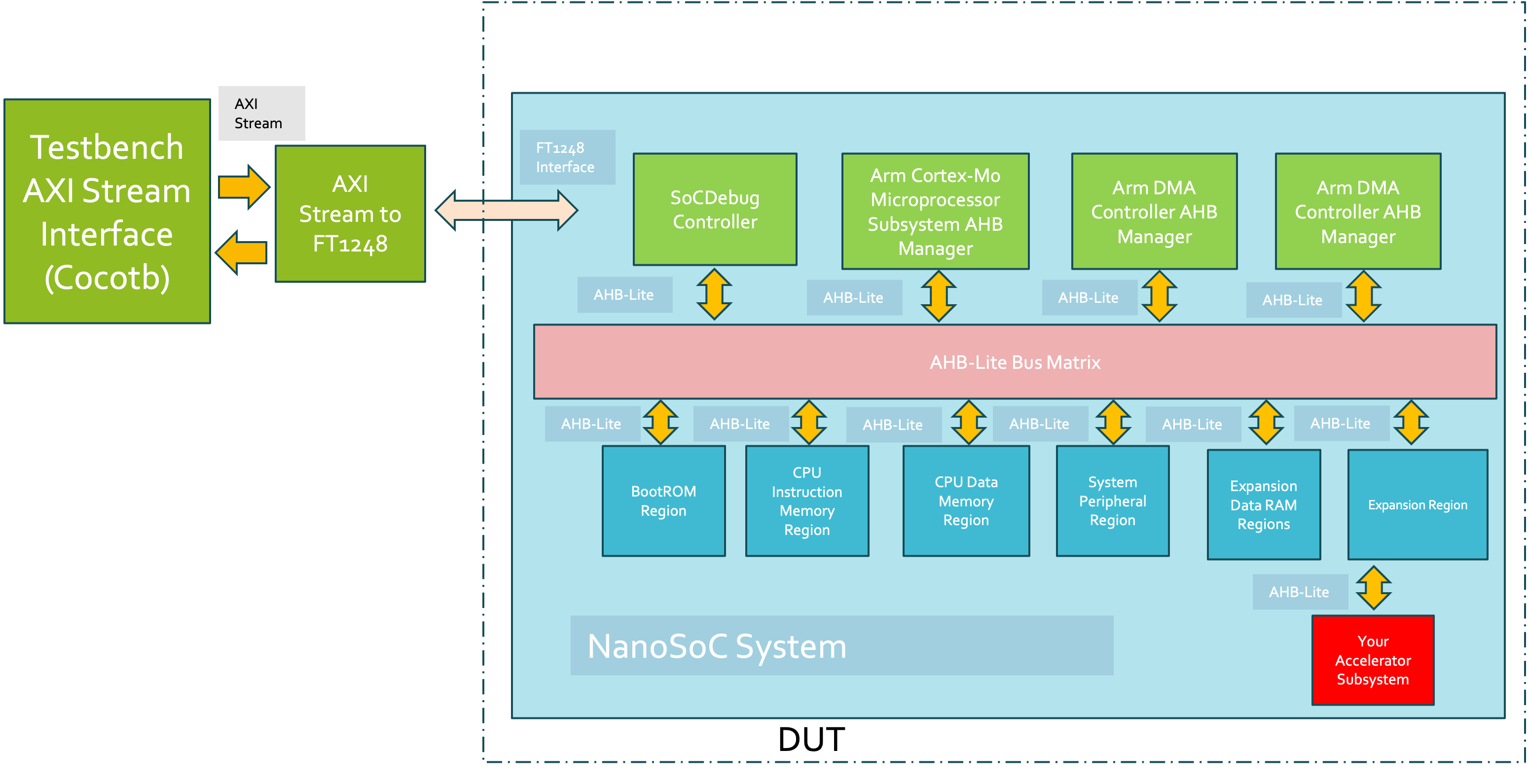

To perform the System Test, the following diagram shows the proposed structure of the test environment:

The main concept for this test bench implementation is to drive and monitor the Cocotb AXI stream interfaces into an AXI Stream to FT1248 Interface that is already within the NanoSoC core, this allows the Cocotb test bench to inject ADP commands into the NanoSoC.

Logical Design: Logical verification

Here we will define methods for Gate Level simulations.

Physical Design: Physical verification

Here we will define the various physical verification processes and the tool chain options for them.

Post Silicon : Test board verification

Here we will define the various test board based verification processes including the software services needed.

Team

Additional Project for:

David Mapstone

David Mapstone

XHB-400: AXI4 to AHB-Lite Bridge

XHB-400: AXI4 to AHB-Lite Bridge

Comments

Update on this work project

Hi,

It would be great to get an update on this work project.

John.

Two years on

We are hoping to re-start this activity as part of nanoSoC v3 and the refactoring of the nanoSoC flows.

Add new comment

To post a comment on this article, please log in to your account. New users can create an account.