People

Projects

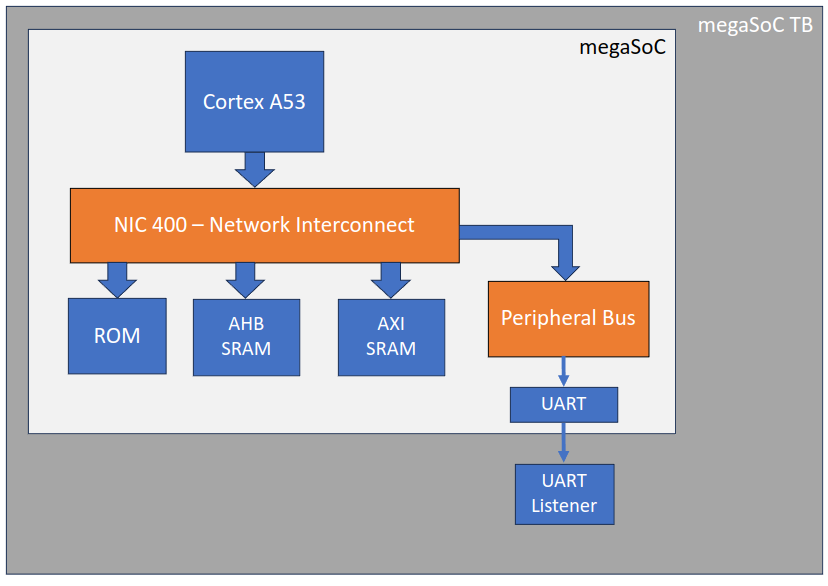

There is growing interest within the SoC Labs community for an Arm A-Class SoC that can support a full operating system, undertake more complex compute tasks and enable more complicated software directed research. The Cortex-A53 is Arm's most widely deployed 64-bit Armv8-A processor and can provide these capabilities with power efficiency.

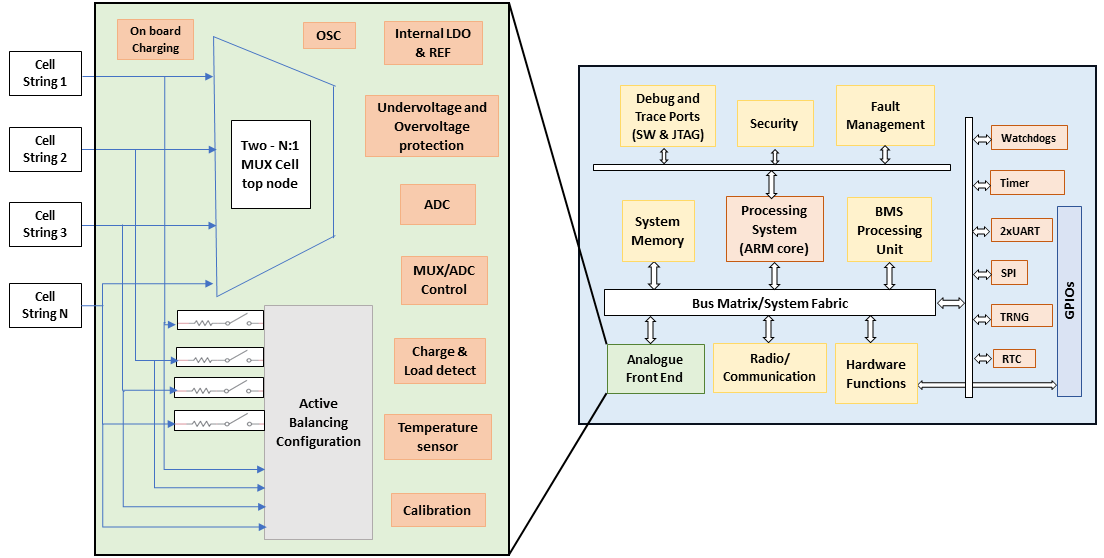

Battery storage systems are an important source for powering emerging clean energy applications. The Battery Management System (BMS) is a critical component of modern battery storage, essential for efficient system monitoring, reducing run-time failures, prolonging charge-discharge lifecycle, and preventing battery stress or catastrophic situations. The BMS performs functionalities such as data acquisition and monitoring, battery state estimation, cell equalization, and charge protection, making it computationally intensive to manage large scale battery storage.

CMOS image sensors (CIS) play a crucial role in the imaging industry. CIS produces low-quality images in low-light conditions. Single Photon Avalanche Diode (SPAD) is a device used for low-light imaging because of its ability to detect single photons of light. To detect a single light photon, SPAD is biased above its breakdown voltage (Gieger mode). When the photon hits the active area during Geiger mode, a significant reverse current (avalanche current) is observed.

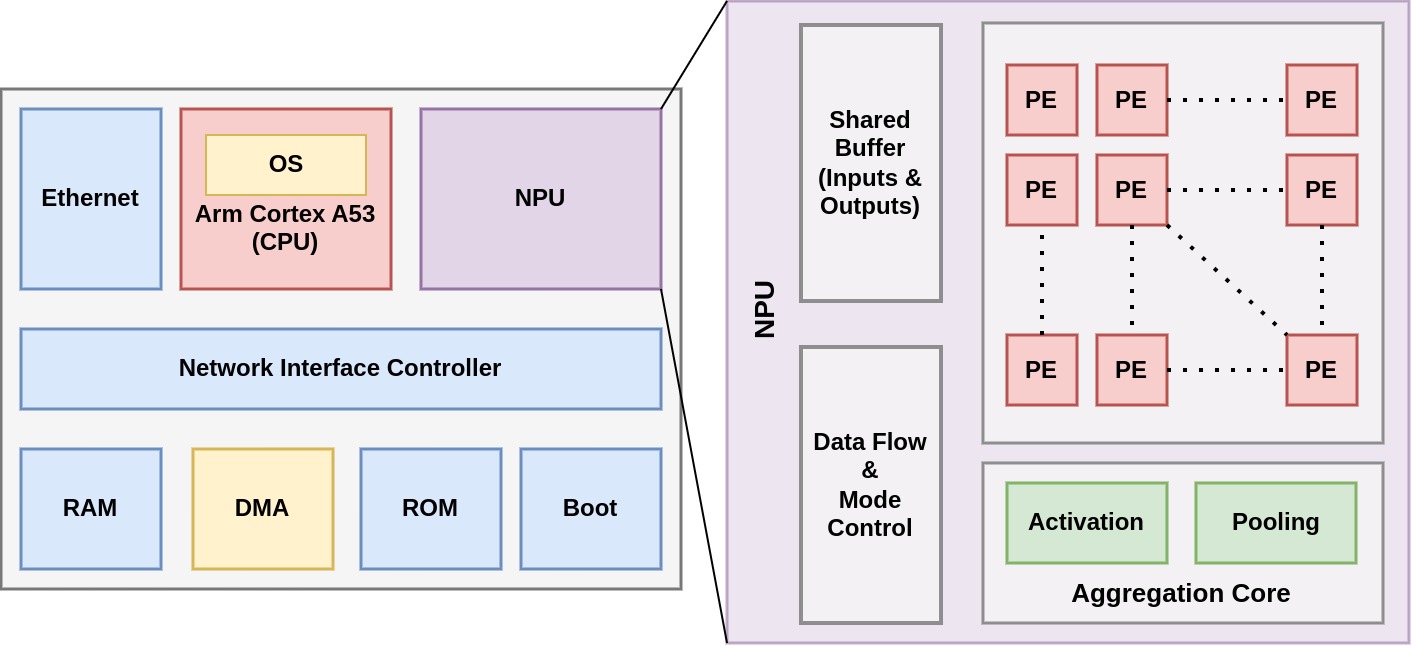

Modern Convolutional Neural Networks (CNNs) are known to be computationally and memory costly owing to the deep structure that is constantly growing. A reconfigurable design is crucial in tackling this difficulty since neural network requirements are always evolving. The suggested architecture is adaptable to the needs of the neural network.

Daniel Newbrook

Daniel Newbrook

Rashi Dutt

Rashi Dutt

Amit Acharyya

Amit Acharyya