Projects

Articles

Interests

Design Flow

Technology

Authored Comments

| Subject | Comment | Link to Comment |

|---|---|---|

| Transition from FPGA to System on Chip design |

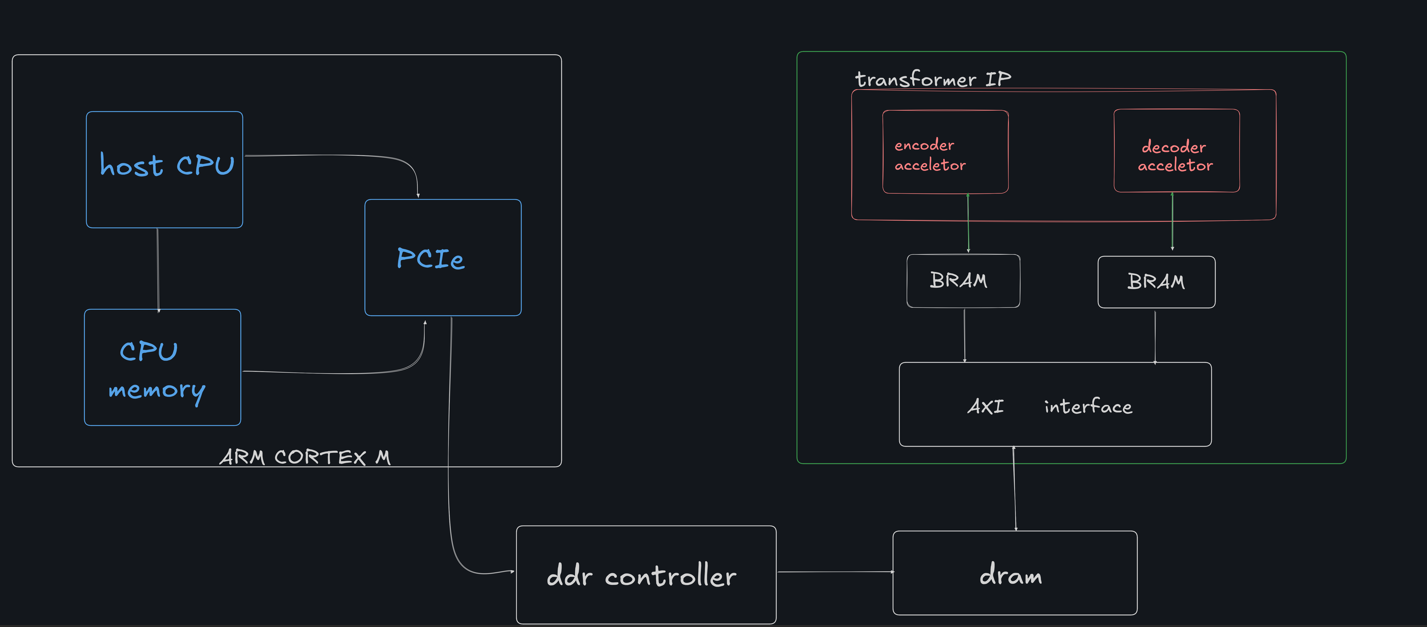

As you develop the design options for the communication protocols between various parts of the SoC you should consider the necessary SoC infrastructure beyond the FPGA implementation when the project moves towards the stages that will 'generate a complete RTL to GDSII flow, enabling the tape-out of our accelerator on a 65nm technology node'.  In later stages there is no separation between PS and PL parts. The operational characteristics of BRAM are different than those of actual on chip 65nm SRAM blocks. In the diagram above the interaction between the DRAM (do we assume this memory is off chip, not on the same ASIC die as the main system?) and the memory (SRAM blocks) close to the transformer IP needs a clearer data movement strategy for the SoC. The current taped out nanoSoC designs on 65nm mode using nanoSoc reference design considers for small data volumes and small accelerators the on chip SoC architecture and has used a variety of DMA approaches. Depending on the model sizes you are planning a more capable architecture may be required. You might want to look at last year's entry from IITH and the comment I made about on chip memory requirements. I hope this helps. |

view |

| Reconfigure FIFO to interface with ADC |

Hi, I was just trying to understand how your activity to reconfigure FIFO to interface with ADC might relate to Daniel's activity on ADC Integration in nanoSoC? Look forward to hearing from you. |

view |

| Welcome to SoC Labs |

Hi, I am glad you managed to sign up. We look forward to hearing from you. |

view |

| Progress on Milestones |

Hi, I hope you had a good summer break. How are things progressing on the project milestones? We look forward to hearing from you. |

view |

| Welcome |

Great to have you join SoC Labs. Looking forward to developing some collaboration projects together. |

view |

| FIFO to interface with ADC |

Hi, I was just trying to understand how your activity to reconfigure FIFO to interface with ADC might relate to Daniel's activity on ADC Integration in nanoSoC? It might be worth exchanging a few details with Daniel Newbrook. Look forward to hearing from you. |

view |

| My mistake |

Sorry about that, I think it is Neil Joseph working on the FIFO and also I was not clear that I was meaning Daniel Newbrook from here at Southampton. |

view |

| Project structure with AAA and nanoSoC |

I think you have been working up to now using the Design Start version of the arm IP. I have seen some comments about looking at the HellFire SoC implementation as that also used the Design Start version of the M0 CPU. Hopefully, now that you have AAA access, you can utilise the full AAA arm IP within a Project structure such as the one we have made available with nanoSoC. If you need any help with this please do let us know. |

view |

| Signal Processing |

Meredith, It would be great to understand any specific areas of interest within Signal Processing you are investigating. Are you looking to develop some new algorithm or new compute architecture to execute existing known functions. From a SoC perspective, last year the focus of nanoSoC was supporting development of custom accelerators that hopefully allow a more efficient execution environment than an alternate software-based implementation of the same algorithm running on the arm cpu using a standard SoC and memory architecture. Most projects were working on Machine Learning/Artificial Intelligence. This year we are looking at mixed signal but many of the design constraints are similar. Data movement through the SoC and where you can take advantage of parallelism. Hopefully some of the projects/teams in this years contest might be of interest to you? We look forward to hearing from you. |

view |

| SoC Labs in Canada |

I am just letting you know that we have some news in terms of the local activities we are working on the help SoC Design activities in Canada. We have a new collaboration project (here) working with Semiconductor Education Alliance partners to help develop a range of local activities in Canada. You might want to join this project and hear about what is being developed?

|

view |

Comments

Hi John,Thank you so much…

Hi John,

Thank you so much for the warm welcome to the community. Sure I would love to learn more. We can have a meeting at your convenience and discuss it. Let me know which times and dates work for you.

Add new comment

To post a comment on this article, please log in to your account. New users can create an account.