Monitoring and enhancing plant growth in space ecosystems

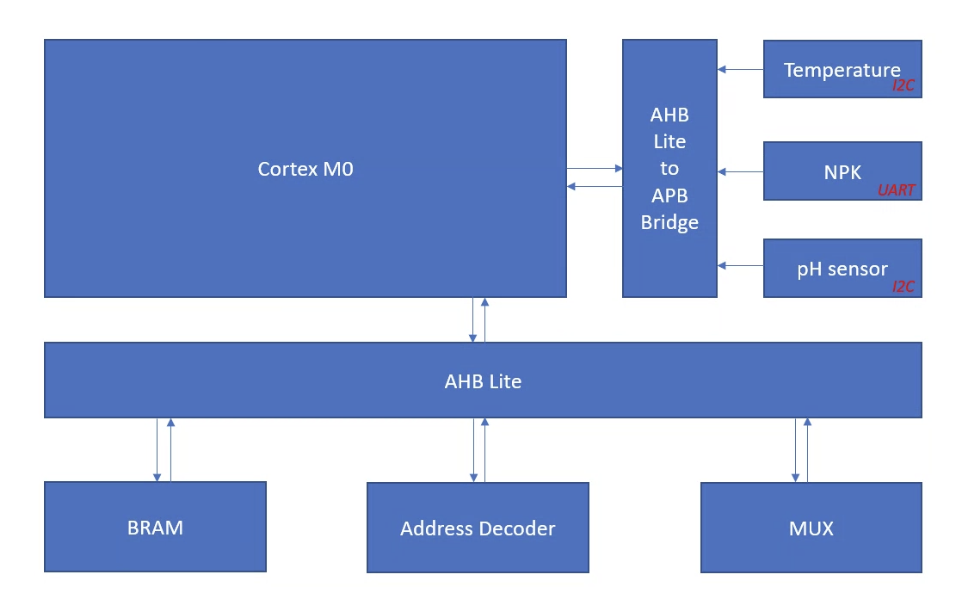

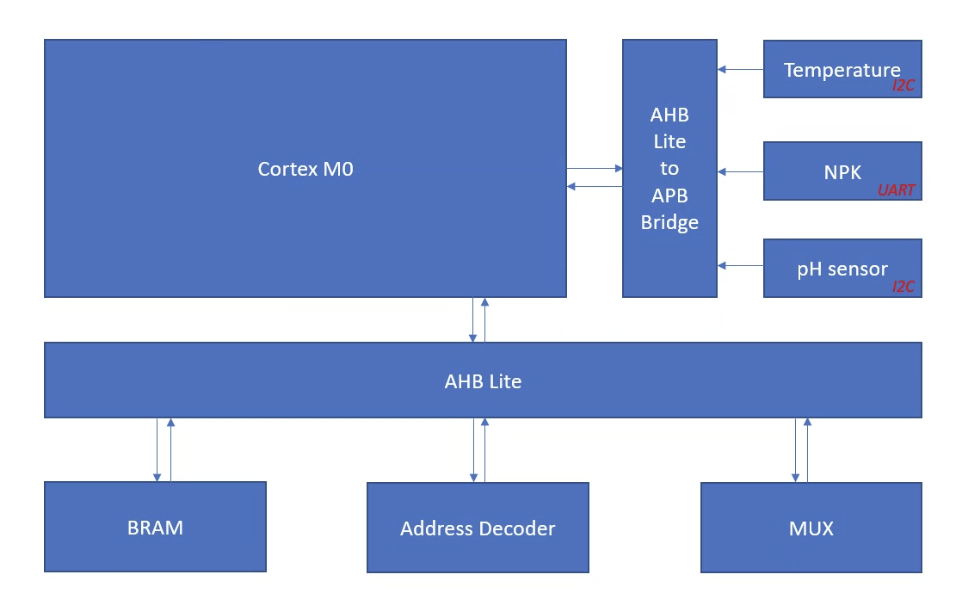

This project focuses on developing a plant growth monitoring system for space exploration missions using the ARM Cortex-M0 microcontroller core. The projects aim to develop a SOC based on ARM M0 core for interactive plant monitoring by interfacing AHB lite, GPIO, timers, and communication protocols such as UART, I2C, SPI, and co-processors. This project also proposes two co-processors for interactive plant monitoring and control. One AI co-processor for classification and prediction of plant and environmental data. Another coprocessor acts as a sensor gateway to control the data from various sensors. The system aims to provide real-time data on environmental parameters crucial for plant growth, especially in space, enabling users to monitor and optimize the conditions for their plants' health and productivity. The objective is to create an efficient solution to monitor and optimize plant growth in the unique environment of space. The system integrates sensors for measuring temperature, humidity, light intensity, CO2 levels, and nutrient availability, specifically designed for space applications, with the ARM Cortex-M0 core. Firmware is developed using the embedded C programming language to interface with the sensors, collect real-time data, and process it for plant health and growth monitoring. A user-friendly interface makes the visualization of plant growth data and environmental factors possible. The ARM Cortex-M0 core enables remote control of environmental variables, including temperature and humidity, optimizing plant growth based on real-time data. The project also emphasizes power optimization, maximizing operating duration on constrained power resources in space by utilizing low-power modes of the ARM Cortex-M0 processor. The anticipated results include a fully functional system for tracking plant growth, real-time environmental parameter monitoring, remote control capabilities, and adequate power management. Research, sensor integration, firmware development, user interface design, remote monitoring and control implementation, power optimization, documentation, and project completion are all covered in the twelve-week project timetable. This project's successful completion will advance knowledge of how plants grow in microgravity and aid efforts to colonize space in the future. It will also increase the viability of long-duration space trips.

Project Milestones

-

Milestone #1

Target Date -

Milestone #2

Target Date -

Milestone #3

Target Date -

Milestone #4

Target Date -

Milestone #5

Target Date -

Milestone #6

Target Date -

Milestone #7

Target Date -

Milestone #8

Target Date -

Milestone #9

Target Date -

Milestone #10

Target Date -

Milestone #11

Target Date -

Milestone #12

Target Date -

Milestone #13

Target Date

Cortex-M0

Cortex-M0

Comments

Update on Milestones

Hi,

As we are now into the start of October it would be good to get an update on your milestones at the end of September.

We need to understand if it is likely you will be making progress so we can progress a tape out.

If you need any help or support for the project please let us know.

We look forward to hearing from you.

Updates on Milestones

Hi,

Thank you for reaching out, We will be updating our dashboard soon so that the information is available for anyone searching it. We will be adding our milestones and other updates soon. We look forward in collaborating with other projects out there and complete this as a collective effort.

Collaboration

Hi,

That is great, we look forward to the update. In terms of collaboration, the team from Sydney and Obafemi Awolowo look to have similar requirements for the overall SoC design. We will look to arrange a collaboration call with you all.

Have a look at Sydney and what they have shared so far.

We look forward to hearing from you.

Collaboration

It was good to meet you on the video collaboration call today. As we discussed on the call it would good in the coming week to:

If we have a clearer view of these things then the project will hopefully move forward more quickly.

We look forward to hearing from you.

Progress on nanoSoC.

The 2023/24 version of the nanoSoC reference design has been used to tape the following projects with custom accelerators and will hopefully give you some help in developing your own project.

Fast-kNN: A hardware implementation of a k-Nearest-Neighbours classifier for accelerated inference by Epifanios Baikas

Hell Fire SoC by Srimanth Tenneti

The die from the ASIC fabrication are back from manufacture and are being tested using the nanoSoC test board.

If you need any help with your project please let us know.

John.

Sensor integration

Hi, Good to see you have resubmited this for the current contest.

Is the sensor frontend going to be an analog subsystem in the SoC or are you planning to use external components for this?

It could be good to get a sense of your design if you could add a block diagram of what you are planning to implement including which components are part of the SoC and what are external interfaces

Design of your sensor gateway

Hi,

It would be helpful to understand a little about your proposed sensor gateway.

Daniel has now published a mixed signal subsystem reference design project to extend the nanosoc reference design to add analog to digital conversion using the APB peripheral bus.

Hopefully this will help you with your Architectural design.

Design of your sensor gateway

Daniel has now updated the mixed signal subsystem reference design project, you might want to follow that project to help you in your own Architectural Design.

Added the Project Details

Hi, thank you for commenting on our project. We are going to add the block diagram of our project which we are planning on implementing using ARM Cortex M0 and we are also looking into incorporating NanoSoC into our project after going through the basic of the NanoSoC system

Setting initial milestone

It would be good to see you plan out your initial milestones. You can follow some of the generic design flow stages or define your own.

The generic flow Architectural Design stage currently has three sub-stages:

Specifying a SoC

Work through the items needed to specify the highest level of design for the SoC. Daniel above asks some for a block diagram which always helps convey your design.

IP Selection

Pick the IP parts from the Technology section. You have listed the main M0 processor IP. What IP will you adopt for other functions, eg. will you use the PL011 UART IP block and will you adopt the APB bus? You might also want to think about your Project Structure and other high level Design Flow considerations.

Verification

You should start to think about how you will validate your SoC design. Creating verification and validation assests as you develop the design is a good working practice.

You should find some helpful examples from some of the other SoC Labs projects.

Happy to help and answer any questions.

Updates to milestones (end of May 2024)

Hi,

It would be good to get an update on your milestones at the end of the month.

John.

Nanosoc Configuration + ADC

Hi,

We've just updated the nanosoc accelerator project repository, there is now a new way to configure nanosoc including how to include the ADC's.

If you go into the nanosoc_tech directory there is a file nanosoc.config. If you add text after any of the

ADC_x_INCLUDE =then the APB bus will be configured for an ADC, and the verilog-ams model of the ADC will be included (this is not synthesizable for FPGA or ASIC - we're working on making this available soon). There is also a test for the adc subsystem called adc_tests. This can be run from the nanosoc_tech directory withUnfortunately at the moment, synopsys VCS is the only supported simulator for the ADC, but we are working on this

Daniel

Add new comment

To post a comment on this article, please log in to your account. New users can create an account.