Projects

Articles

Interests

Design Flow

Technology

Authored Comments

| Subject | Comment | Link to Comment |

|---|---|---|

| Post Tape Out Validation and Test Board |

It is great to get the design off for tape out and awaiting the die back from the foundry. How are you getting on with the milestones for the post tape out validation and the use of the new nanoSoC test board? |

view |

| Adding initial milestones |

Hi, Great to see the project live. It is very easy to add the initial milestones and you can come back as each milestone progresses and make updates. IITH are a good example of milestones in their project https://soclabs.org/project/real-time-edge-ai-soc-high-speed-low-complexity-reconfigurable-scalable-architecture-deep You can simply select milestones from the generic design flow stages or create any unique milestones. |

view |

| This item needs a refresh based on nanoSoC tape out experience |

Hi, We should refresh this item based on nanoSoC tape out experience |

view |

| Welcome to the contest. At… |

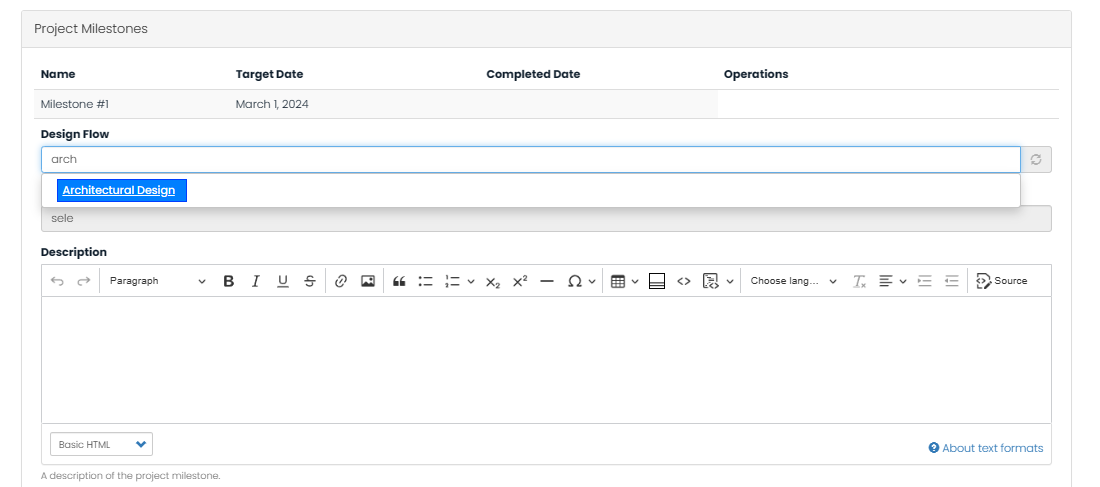

Welcome to the contest. At first look the micro-controller-driven device for collection of real-time data from the environment combined with built-in capability for machine learning is right on target for the contest. It would be good to start to explain the requirements of the collection of real-time data. Daniel has just updated the Architectural Design stage item in the work flow for You can add a milestone for the work. Edit the Project and select the milestone by typing... arch and then it auto completes the design step. Don't forget to save the change.

|

view |

| Source code repository link |

Hi, Is there a link we can add for the source code? |

view |

| Adding new milestones |

It is very easy to add new milestones and you can come back as each milestone progresses and make updates. IITH are a good example of milestones in their project https://soclabs.org/project/real-time-edge-ai-soc-high-speed-low-complexity-reconfigurable-scalable-architecture-deep You can simply select milestones from the generic design flow stages or create any unique milestones. So taking the first steps in the design flow you type 'arch' and it autocompletes the design flow step needed. |

view |

| Adding your first milestone |

Thanks for adding the first milestone on architecture design. I was wondering how you see the decomposition of the system into parts to handle the collection of real-time data from the environment and combining that with built-in capability for machine learning. I was wondering if the external devices would sit on say the APB bus and the machine learning on the main SoC bus? You will see that for the NanoSoC reference and a few examples from contestants the custom accelerator for ML was integrated with a DMA controller on the main bus. How do you see the main functional blocks being separated? |

view |

| Welcome |

Welcome to SoC Labs. I see you have shared an interest in accelerators. Will you be working on the accelerator part of the Data Acquisition SoC design ? There are several projects in last year's contest that should give you some ideas for how to develop this. One thing to consider is the data flow into and out of the custom accelerator logic. Two examples Hell Fire SoC and Fast Knn accelerator have both been taped out in 65nm technology node and may help with your design and also you could also benefit from development of re-usable design assets. Do you have any questions? |

view |

| Next Milestones |

Architectural Design stage currently has three sub-stages:

You should find some helpful examples from some of the other SoC Labs projects. Happy to help and answer any questions. |

view |

| How can we make this more interesting? |

Hi, It seems quite a few of you have declared an interest in Machine Learning. What can we add to this section to make it more interesting? How can we get this thread started and more helpful to you? Any feedback is really welcome. John. |

view |

Comments

Hi John,Thank you so much…

Hi John,

Thank you so much for the warm welcome to the community. Sure I would love to learn more. We can have a meeting at your convenience and discuss it. Let me know which times and dates work for you.

Add new comment

To post a comment on this article, please log in to your account. New users can create an account.