CoreLink NIC-400

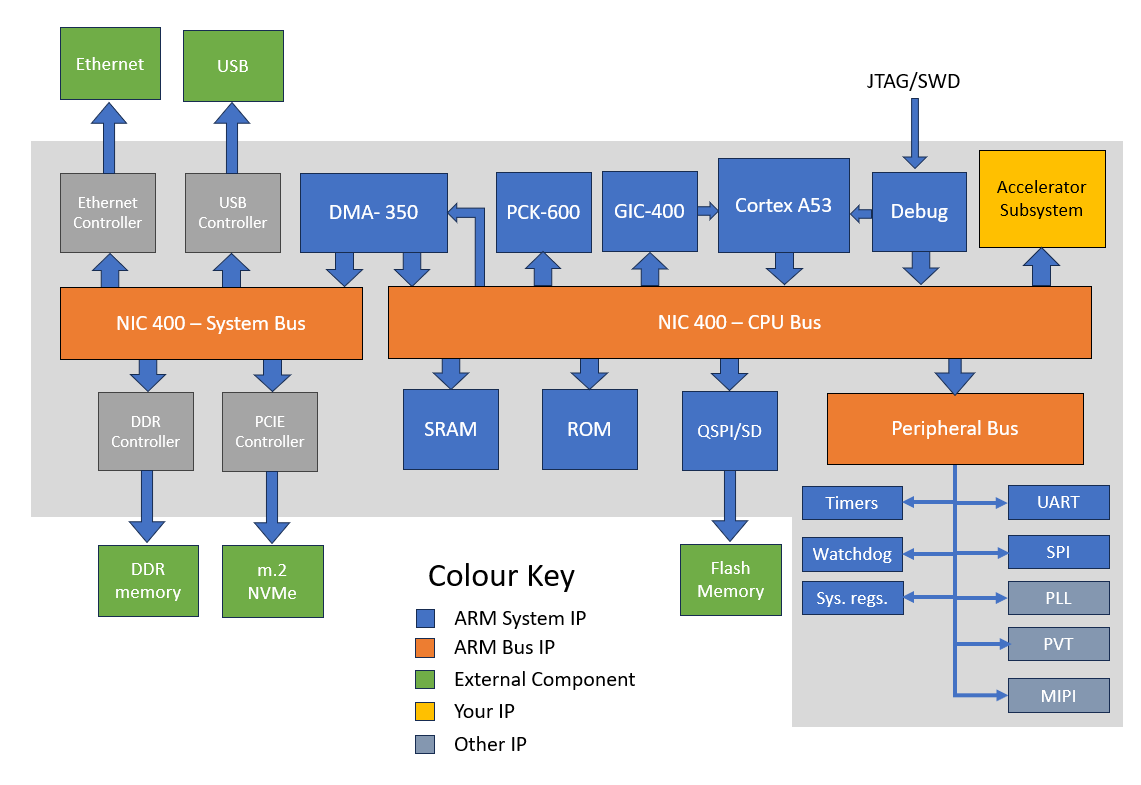

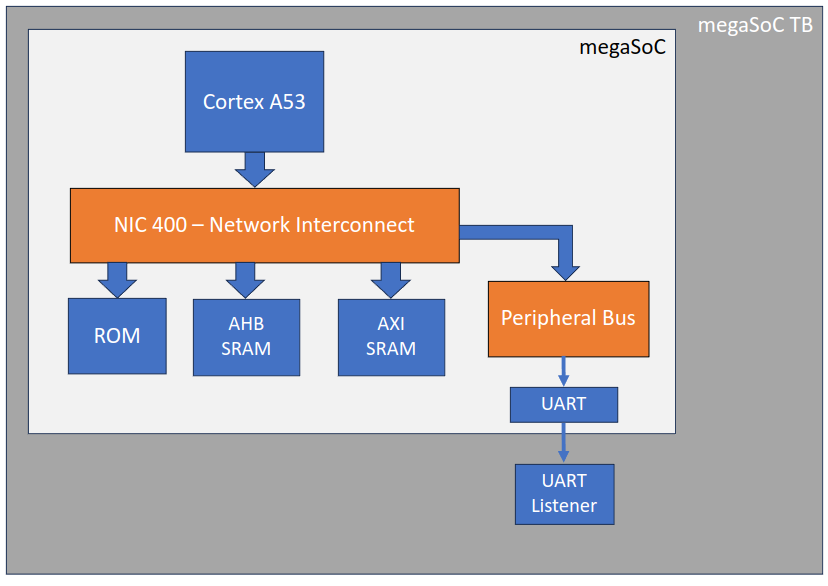

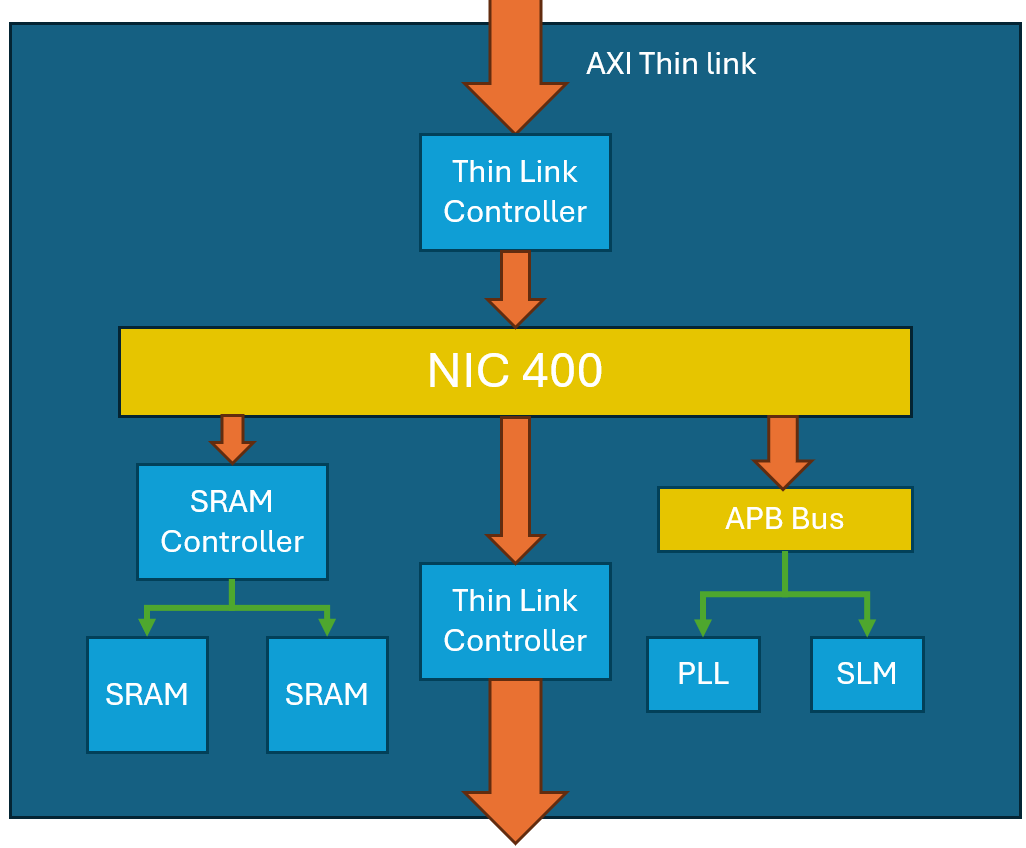

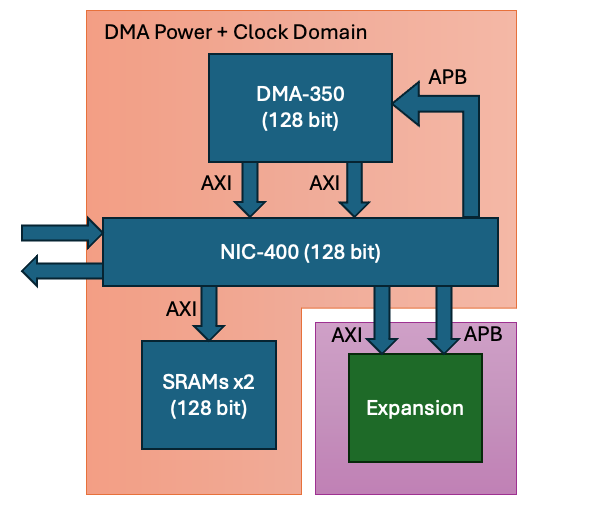

CoreLink NIC-400 can be used to create the Advanced Microcontroller Bus Architecture compliant Interconnect communication path between the functional blocks of the System on Chip. It can be configured in a range of options from a simple AHB to AXI protocol conversion bridge to complex Network On Chip with up to 128 masters and 64 slaves.

The Arm Socrates IP Tooling contains configuration tools that can generate implementations of a CoreLink NIC-400 Network Interconnect. The design of the Interconnect toplogy is changed by configuring the switches and bridges to optimise the flows between the masters and slaves of the SoC. The designer can adjust data widths, clocking, buffering and other parameters to optimise attributes such as wire and gate counts, latency, power consumption, etc. to maximise efficiency to the specific application. Traffic generators can be used to generate transaction flows to validate a specific design.

As the application demands on the SoC interconnect increase addition IP can be added support the flow of data in the interconnect either from standard Arm blocks or ultimately development of a customized Network Interconnect component.

It supports building a SoC with the TrustZone secure and non-secure capabilities as well as options for low power operations.

Explore This Technology

Projects Using This Technology

Add new comment

To post a comment on this article, please log in to your account. New users can create an account.