People

Projects

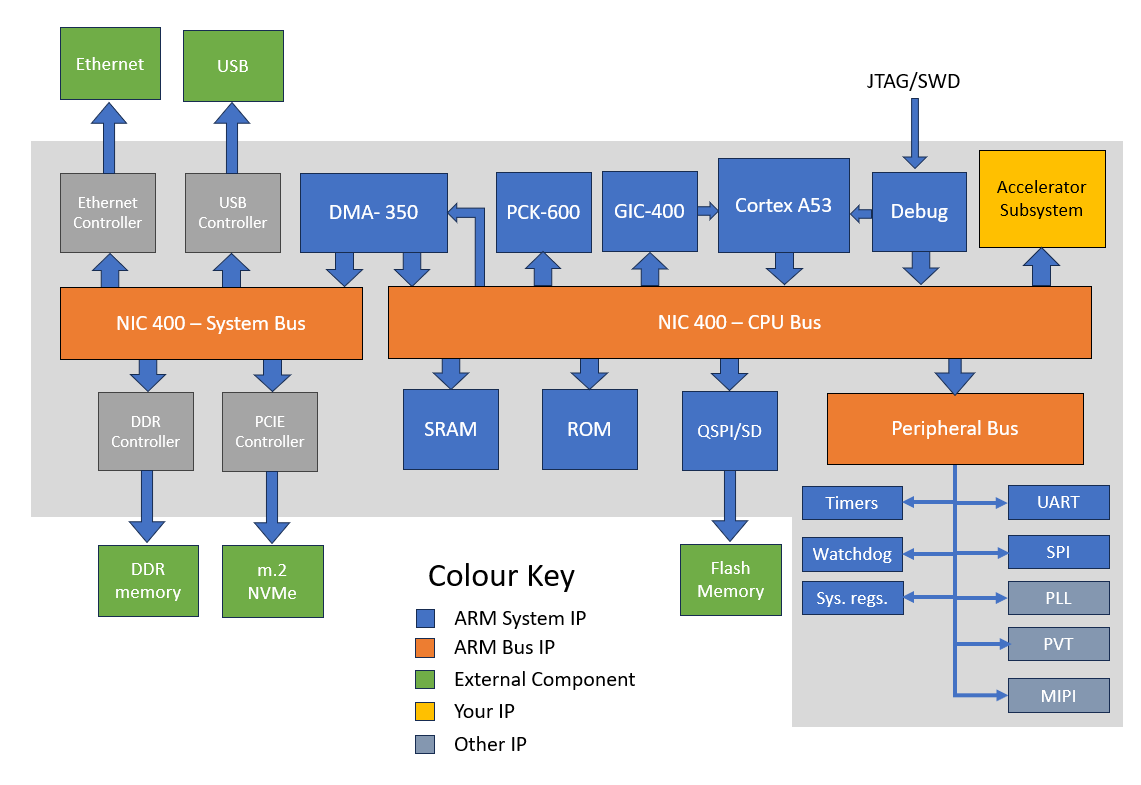

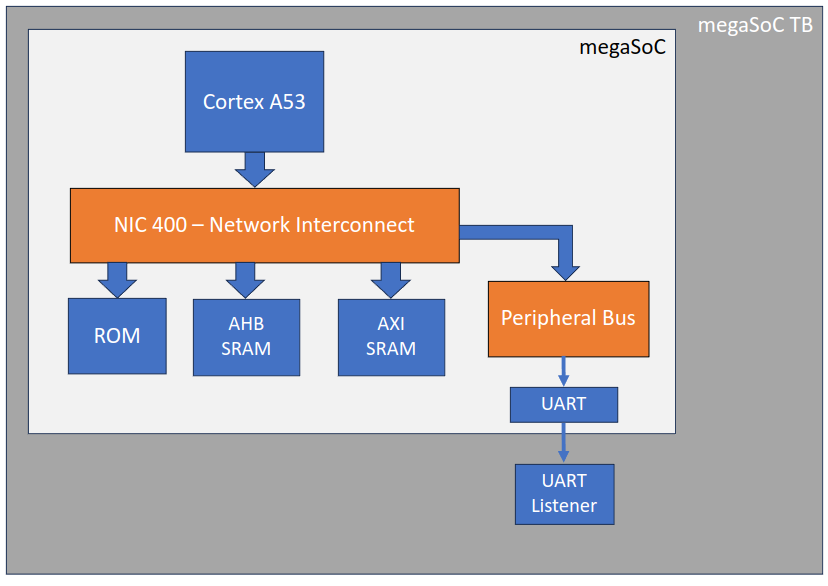

megasoc has been designed to provide a complex SoC component that can 'host' and support the development and evaluation of research components or subsystems. The design allows for seamless transition from FPGA to physical silicon implementation via a pre-verified programmable control system that allows reuse of software and diagnostic functionality to facilitate the configuration, control and diagnostic analysis of research hardware such as custom accelerators or signal processing.

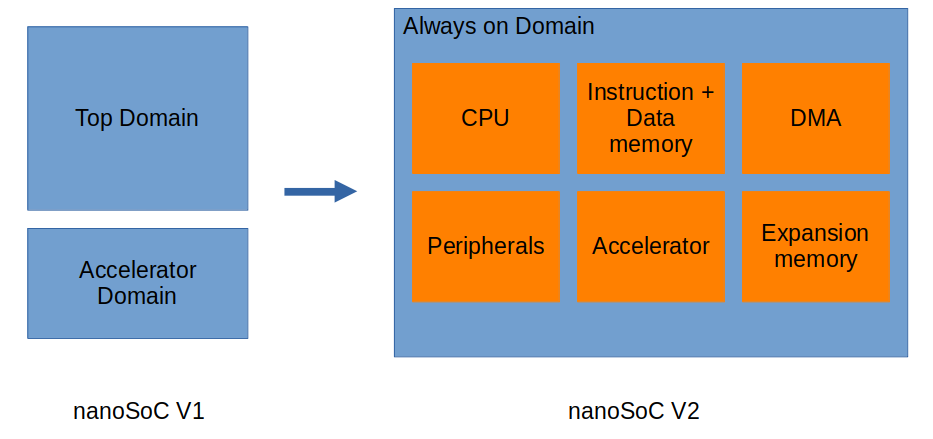

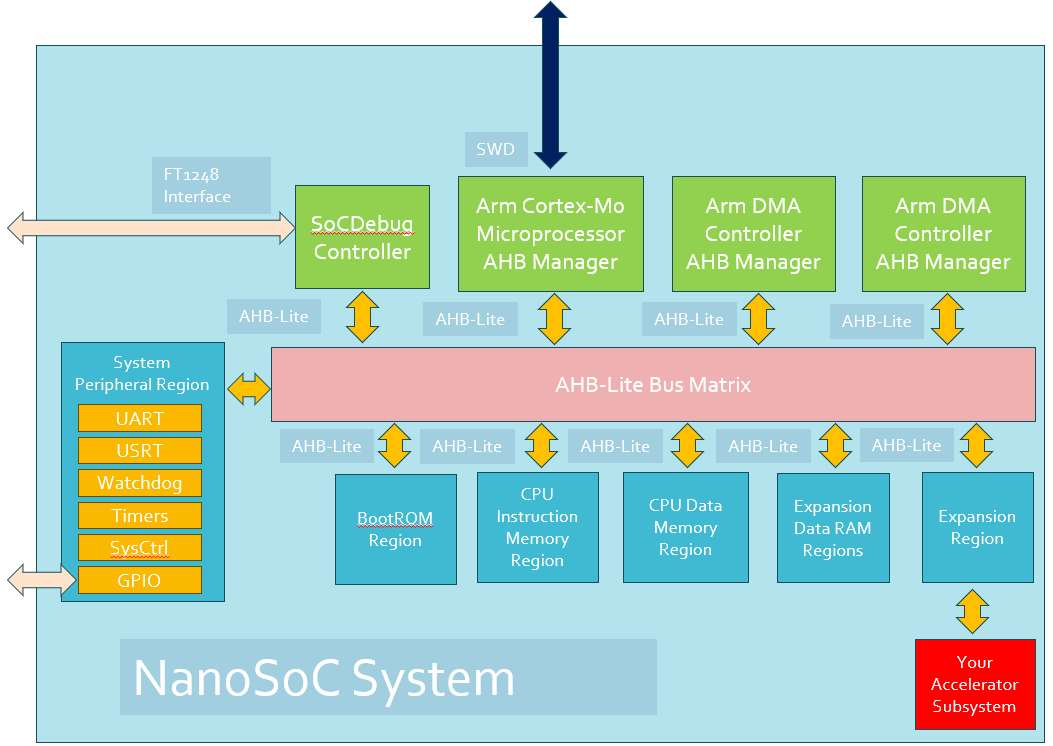

As part of plans for continued development of nanoSoC one area that requires improvement is the power structure of system. The first iteration of nanoSoC contained 2 power domains: the accelerator domain and the remainder of the SoC. Both power domains were connected to external pins to allow connection to separate external voltage regulators and power measurement ICs, as implemented in the first version of the nanoSoC testboard.

There is growing interest within the SoC Labs community for an Arm A-Class SoC that can support a full operating system, undertake more complex compute tasks and enable more complicated software directed research. The Cortex-A53 is Arm's most widely deployed 64-bit Armv8-A processor and can provide these capabilities with power efficiency.

Daniel Newbrook

Daniel Newbrook

David Flynn

David Flynn