View Collaborative Projects

Motivation

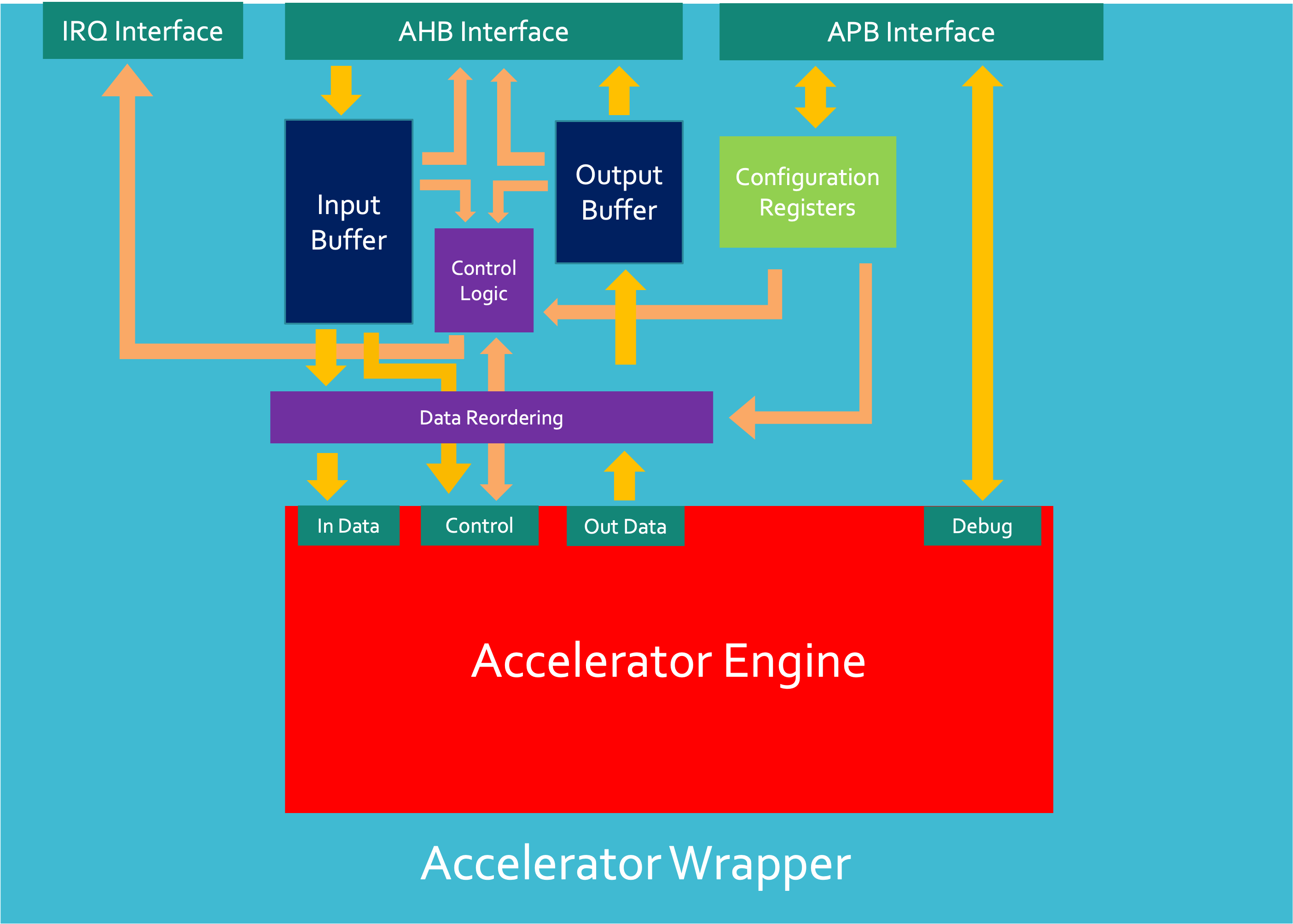

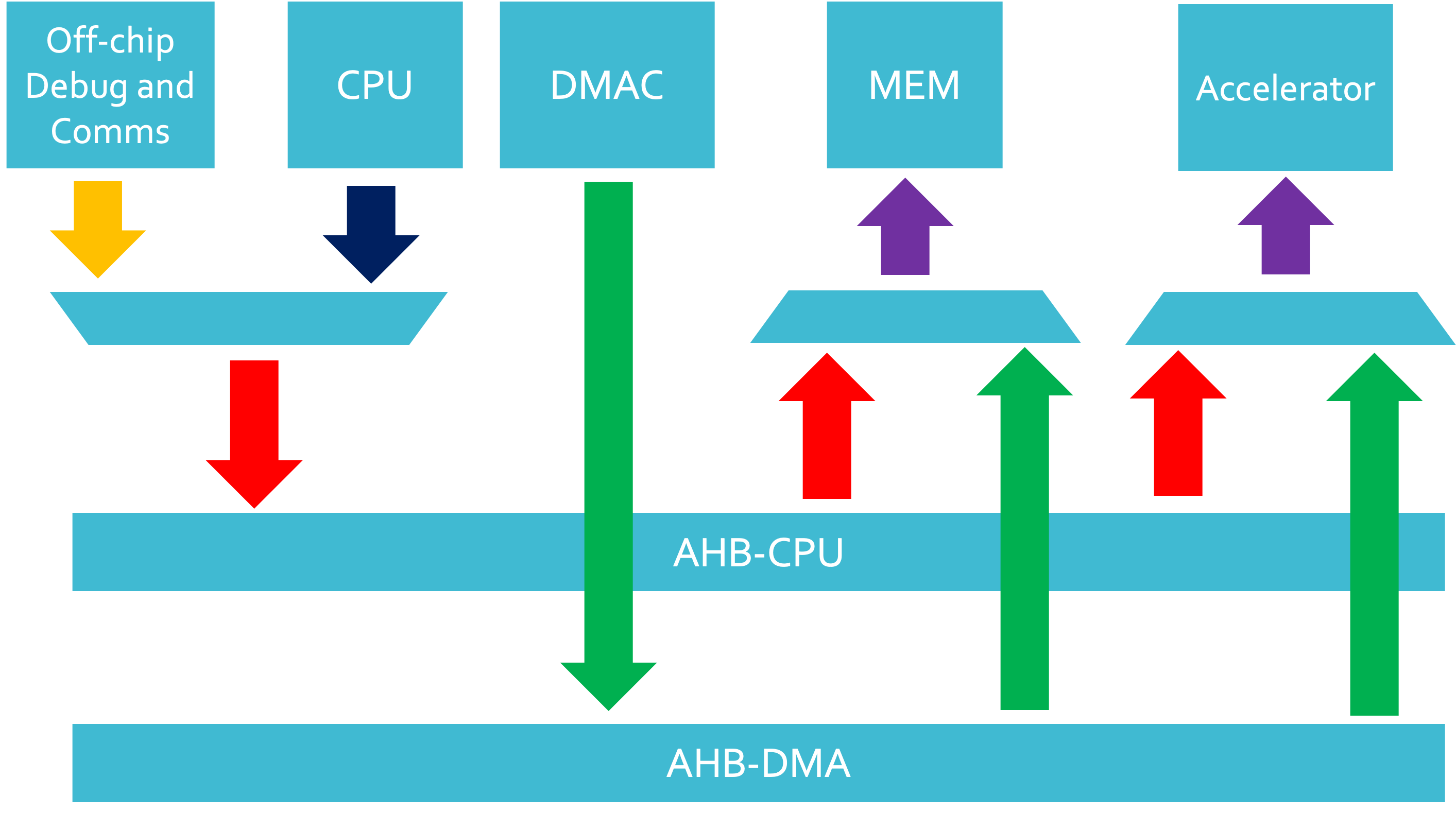

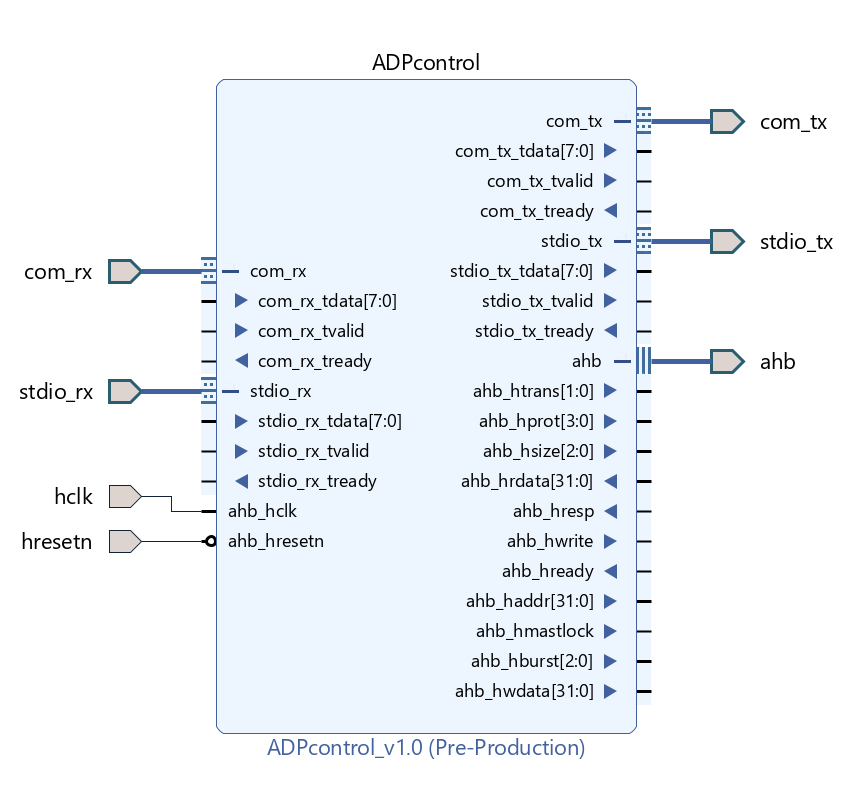

At SoC Labs, we have need of an accelerator to test our SoC infrastructure and confirmation of our accelerator wrapper design to get size and performance information as well as to try and get ahead and uncover potential problems researchers may experience trying to put their IP into the reference SoC.

Specification

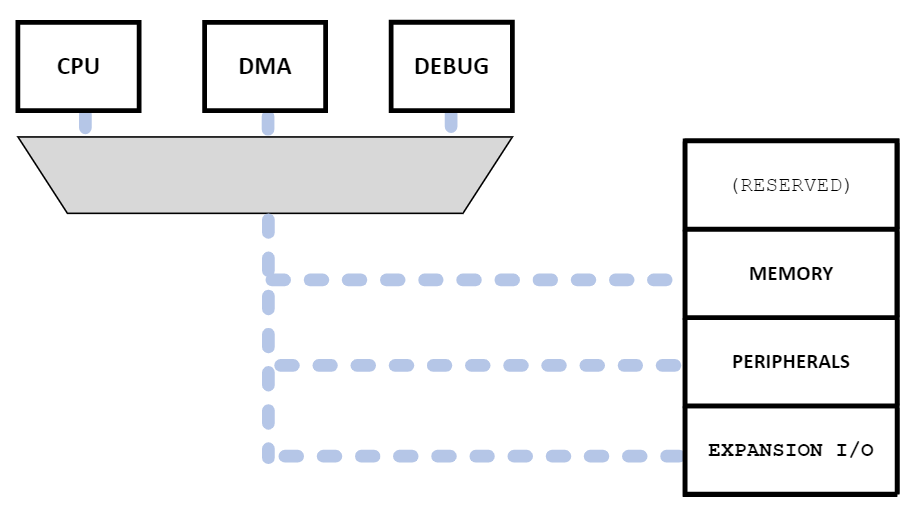

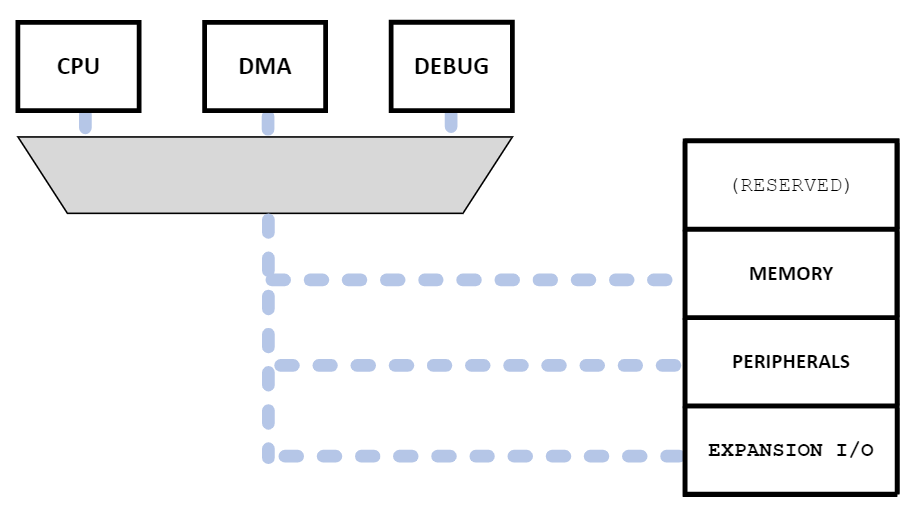

The preliminary design has been broken into two main blocks:

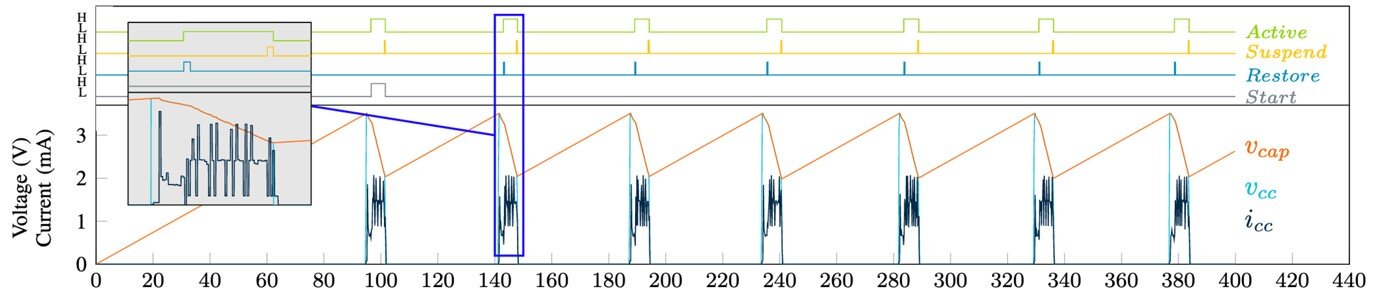

Fused is a full-system simulator for modelling energy-driven computers. To accurately model the interplay between energy-availability, power consumption, and execution; Fused models energy and execution in a closed feedback loop.

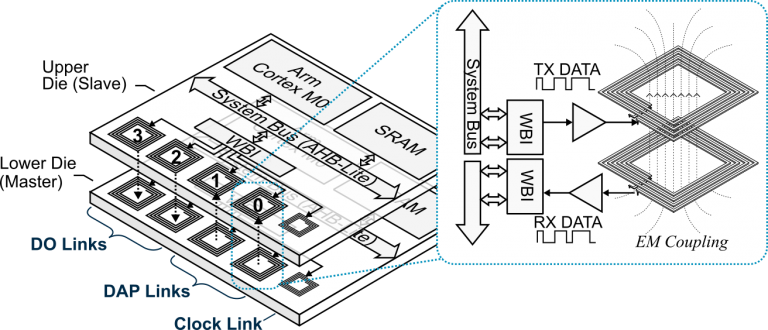

This project developed a 2-tier 3D-stacked Cortex-M0 SoC, in 65nm CMOS technology, with wireless inter-tier power and data transfer through an inductively coupled bus which achieved 20.3Gbps/mm2 data, and 7.1mW/mm2 power transfer simultaneously through a 250 µm channel. At the time of publishing it was the smallest ever reported inductive data and power link.

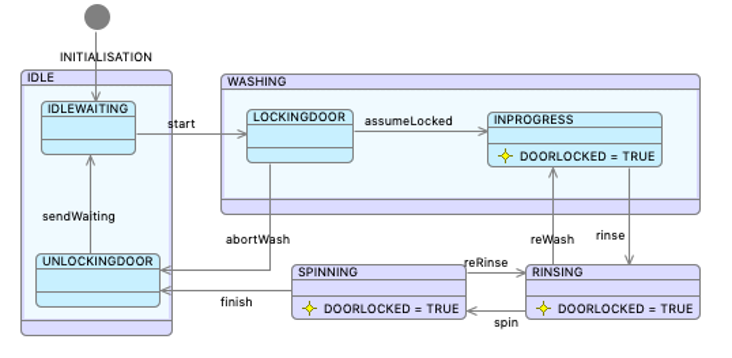

The aim of the project will be to establish the tool chain and flows to demonstrate Event-B refinement to a Register Transfer Level implementation that can target an FPGA implementation. Previous European, EC Information and Communication Technologies FP7 DEPLOY and European Union ICT Project ADVANCE developed VHDL code generation from Event-B models. A number of projects within these and other research programmes have looked at the required process flows. The Rodin Platform is an open source Eclipse-based IDE for Event-B.

David Flynn

David Flynn

David Mapstone

David Mapstone

Daniel Newbrook

Daniel Newbrook

Epifanios Baikas

Epifanios Baikas

Samuel

Samuel

John Darlington

John Darlington

Michael Butler

Michael Butler