Academic Institution

People

Name

Research Area

energy harvesting systems, IoT

Role

Lecturer

Name

Research Area

Low power system design

Role

Consultant

Name

Research Area

Physical and Applied Sciences

Role

Research Systems Manager

Name

Research Area

energy-efficient computing

Role

Professor

Name

Research Area

Intermittent Computing, Energy-aware design

Role

Student

Name

Research Area

Machine Intelligence for Nano-Electronic Devices and Systems, Secure and Resilient Hardware Implementation of AI Modules

Role

Postgraduate researcher

Name

Research Area

Machine Intelligence for Nano-Electronic Devices and Systems | Reinforcement Learning

Role

Postgraduate Researcher

Projects

Collaborative

Active Project

To utilise chiplets for small M-class microcontroller based systems there is a need to extend the range of the AHB standard on-chip bus interconnect. This 'Tidelink' project extends the planned AXI Chiplet controller to support AHB transactions across chiplets.

Collaborative

Active Project

This project demonstrates running the lwIP UDP/IP stack on a MicroBlaze soft processor within an XIlinx PYNQ-Z2 FPGA to create a simple embedded Ethernet communications subsystem. The design integrates a custom Ethernet PHY interface and AXI EthernetLite MAC to enable basic networking functionality. An lwIP echo server runs on the MicroBlaze, while the Zynq Processing System hosts a UART bridge application for host communication. The project is being used to undertake design exploration for soft-core processors in FPGA logic to implement and verify lightweight networking stacks.

Reference Design

Active Project

This project aims to access the user needs and develop the next increment of capability for nanoSoC. It outlines the justification and motives behind the architectural redesign, design flow improvements and code repository refactor. With a number of new subsystems planned for nanoSoC and learning from various projects to date, this version of nanoSOC is expected to provide a much better support for academic projects.

Reference Design

Active Project

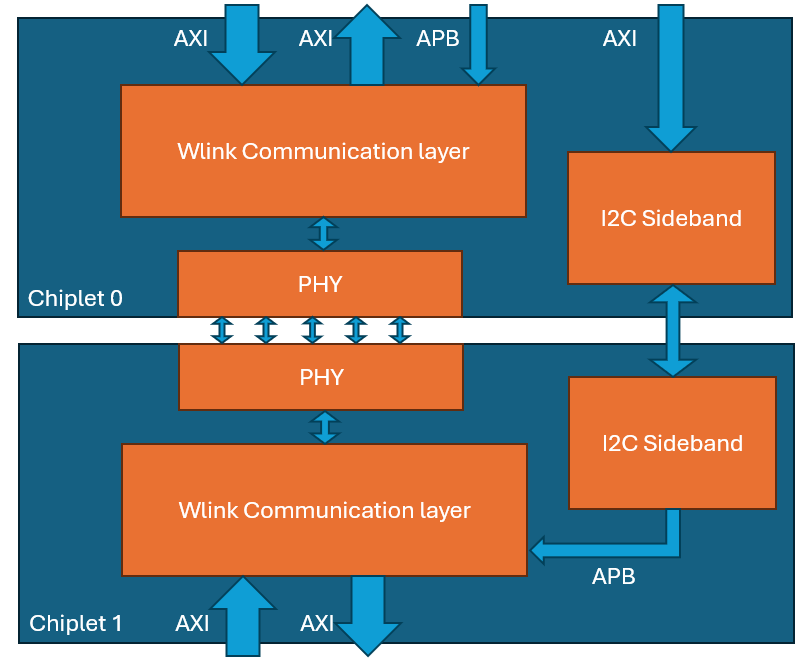

For a chiplet system, you need a communication interface between chiplets. The industry has developed standards that require complicated IPs around UCIe and the CHI interface from Arm. For many academic projects these are probably more complicated than needed . The aim of this project is to produce a simple chiplet communications interface based around the open standard AXI protocol.

The project is hosted here: https://git.soton.ac.uk/soclabs/chiplets/axi-chiplet-controller

David Mapstone

David Mapstone

Daniel Newbrook

Daniel Newbrook