Projects

Articles

Interests

Design Flow

Technology

Authored Comments

| Subject | Comment | Link to Comment |

|---|---|---|

| SoC Labs in Canada |

I am just letting you know that we have some news in terms of the local activities we are working on the help SoC Design activities in Canada. We have a new collaboration project (here) working with Semiconductor Education Alliance partners to help develop a range of local activities in Canada. You might want to join this project and hear about what is being developed?

|

view |

| Custom wrapper file for the ADC |

"Ted (Kezhi) is investigating a custom wrapper file for the ADC, drawing from https://soclabs.org/project/adc-integration-nanosoc" Please reach out and ask for any help you need. An easy way is to simply add a comment on the ADC integration project and Daniel should respond. Asking questions in this way not only helps you but also other people. We are very keen to get people to collaborate on IP blocks and also design flow and environment issues. Look forward to hearing from you.

|

view |

| Interesting paper on FPGA implementations of ML |

Here is an interesting paper on a model to determine FPGA resources for multi-layer neural networks. Part of their conclusions is “LSTM turned out to be very demanding on FPGA computing resources”. Do you have a view on the LSTM implementation you will need for this application?

|

view |

| Potential funding opportunity |

I am not sure if this is of any help but perhaps you can take a look at this call |

view |

| Interest in SoC Labs |

Hello, I see that you have interests in custom acceleration for device based AI/ML as well as sensor data processing. It would be helpful to know what interest you might have in SoC Labs or the arm ecosystem. We look forward to hearing from you. |

view |

| Memory size |

You asked the question on the model size in MB's and the ideal size to target versus the trade off in accuracy. On chip SRAM is a limiting factor in SoC design due to the high cost of the area for SRAM. While the hierarchical memory system for classical compute has been optimised, from the off chip DRAM all the way through the cache levels, it is has not for custom acceleration. One approach we are using to reduce fabrication costs is the use chiplet based SRAM die which can be added to a SoC from a stock of pre-fabricated die as opposed to adding to the die cost of a custom accelerator. Classical compute has caches in low MB. |

view |

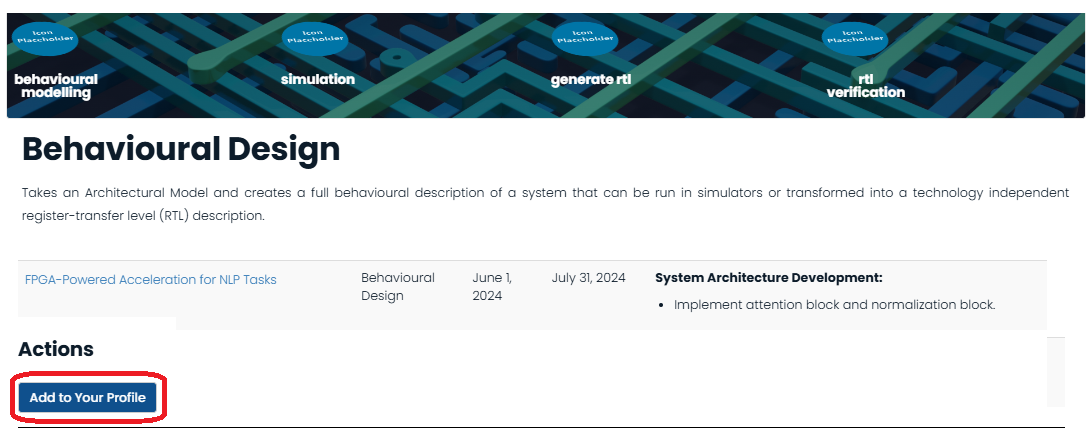

| Adding interests |

Hi, It is easy to add interests as you look at the information on SoC Labs. Just add it to your profile by clicking on the button.

|

view |

| Welcome to SoC Labs |

Thanks for joining SoC Labs. Were you at the IEEE SOCC conference in Dresden or did you just find us on the web? Look forward to hearing from you and finding out how we can collaborate. |

view |

| Workshop on the 17th October |

We have a workshop specifically for North American and Canadian universities arranged with CMC on the 17th October. It would great if you could attend and here about the latest status of SoC Labs activity and also here how to get involved. Canadian Workshop: Make Academic System on Chip Projects Easy via Collaboration and Reusable Design And here is the linkedin announcement Academic System on Chip Projects Made Easy LinkedIn announcement Look forward to hearing from you. |

view |

| Workshop on October 17th |

We have a workshop specifically for North American and Canadian universities arranged with CMC on the 17th October. It would great if you could attend and here about the latest status of SoC Labs activity and also here how to get involved. Canadian Workshop: Make Academic System on Chip Projects Easy via Collaboration and Reusable Design And here is the linkedin announcement Academic System on Chip Projects Made Easy LinkedIn announcement Look forward to hearing from you. |

view |

Add new comment

To post a comment on this article, please log in to your account. New users can create an account.