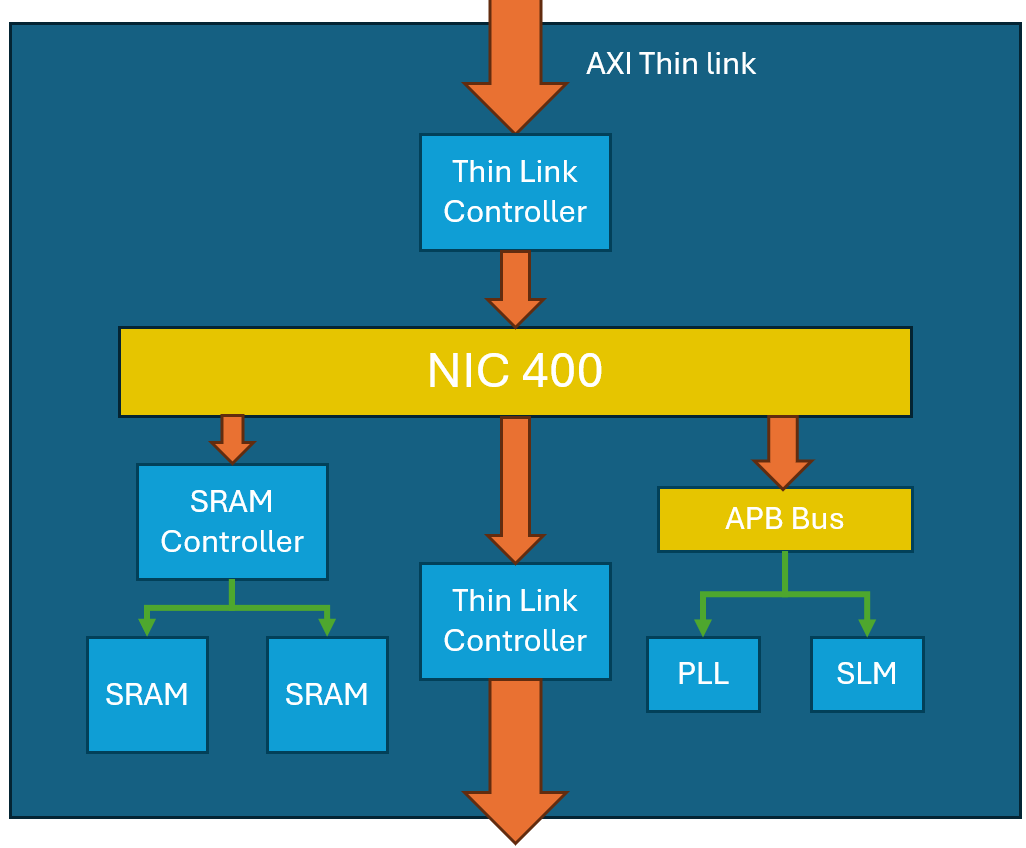

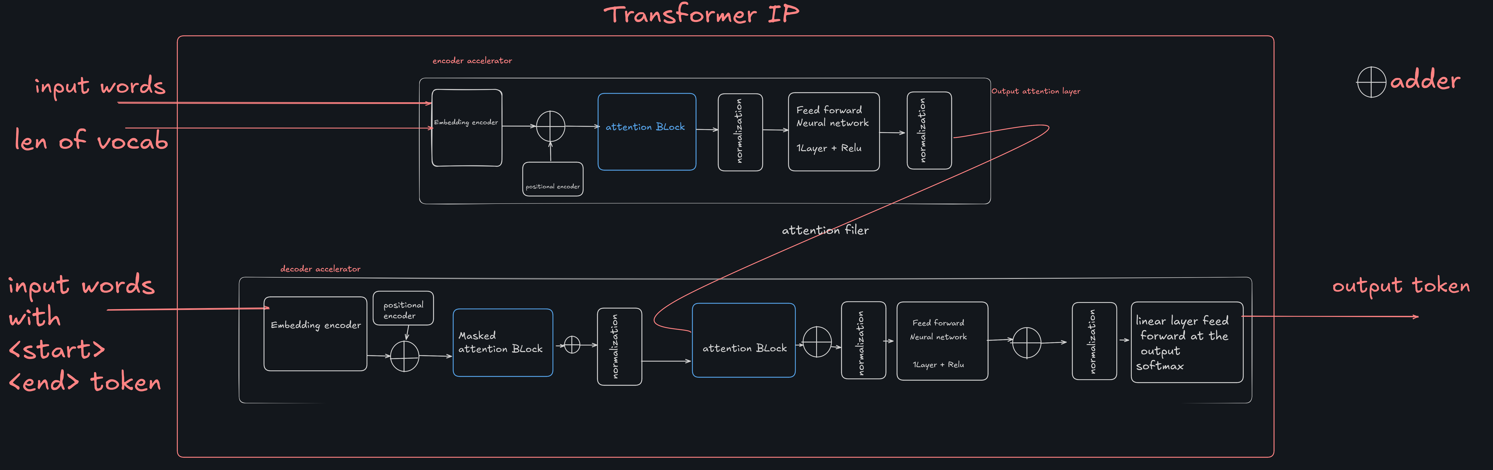

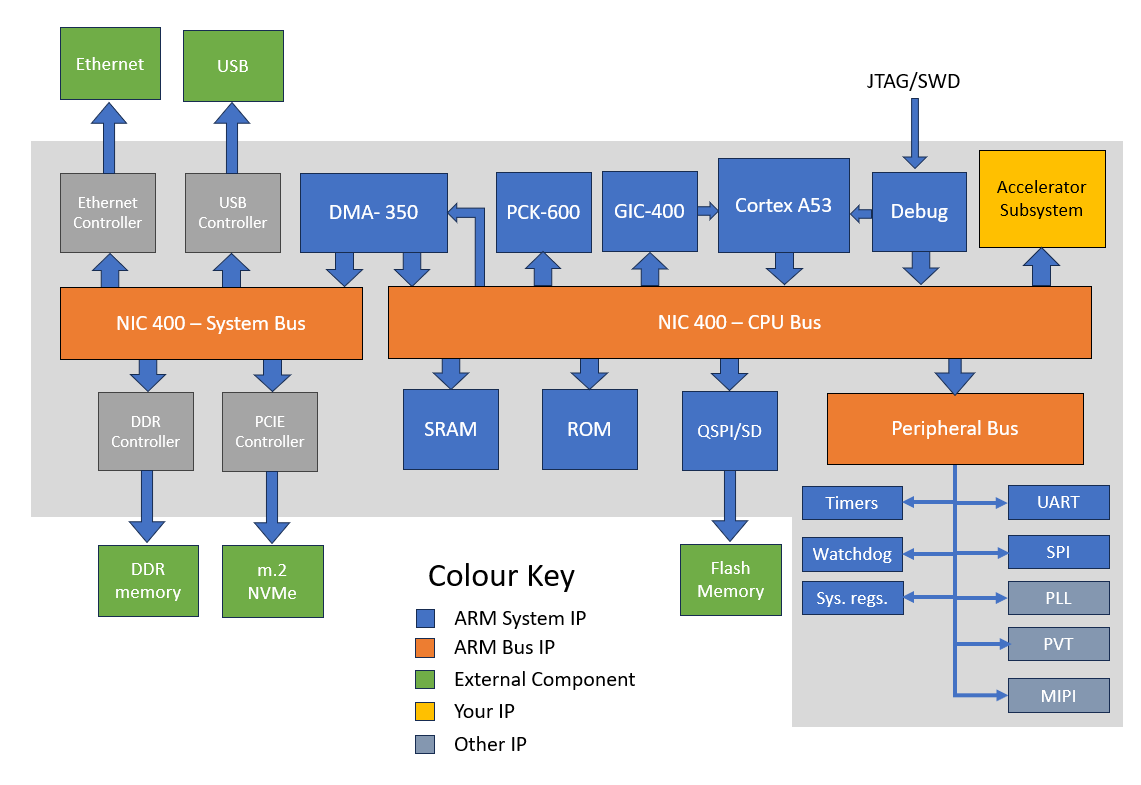

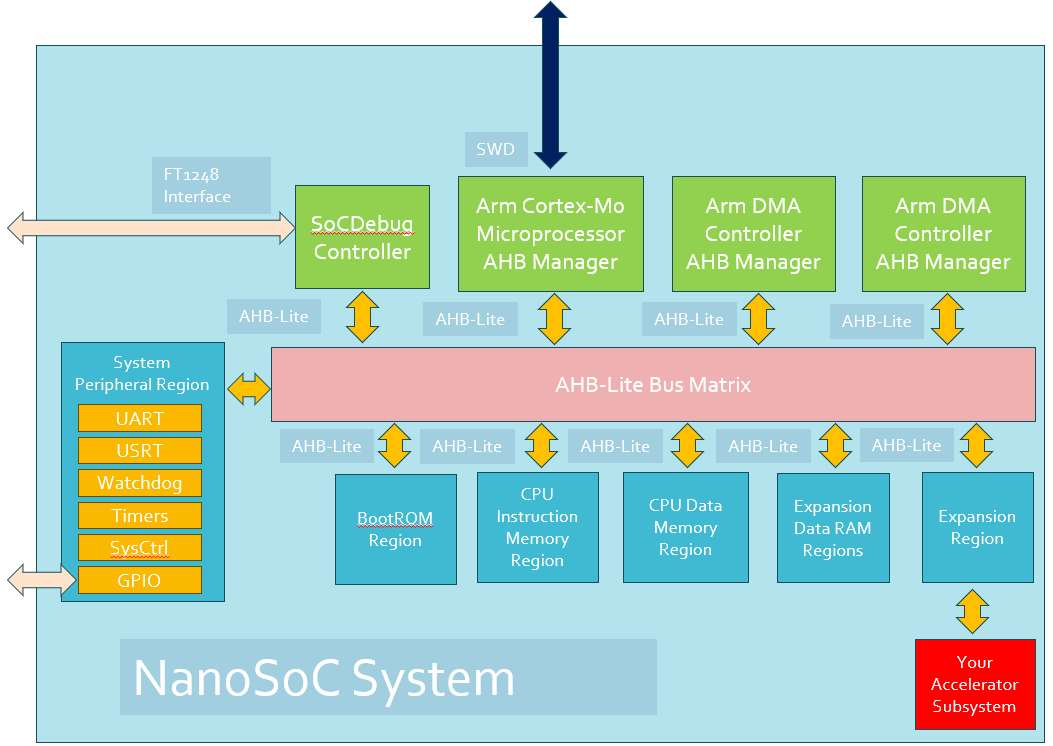

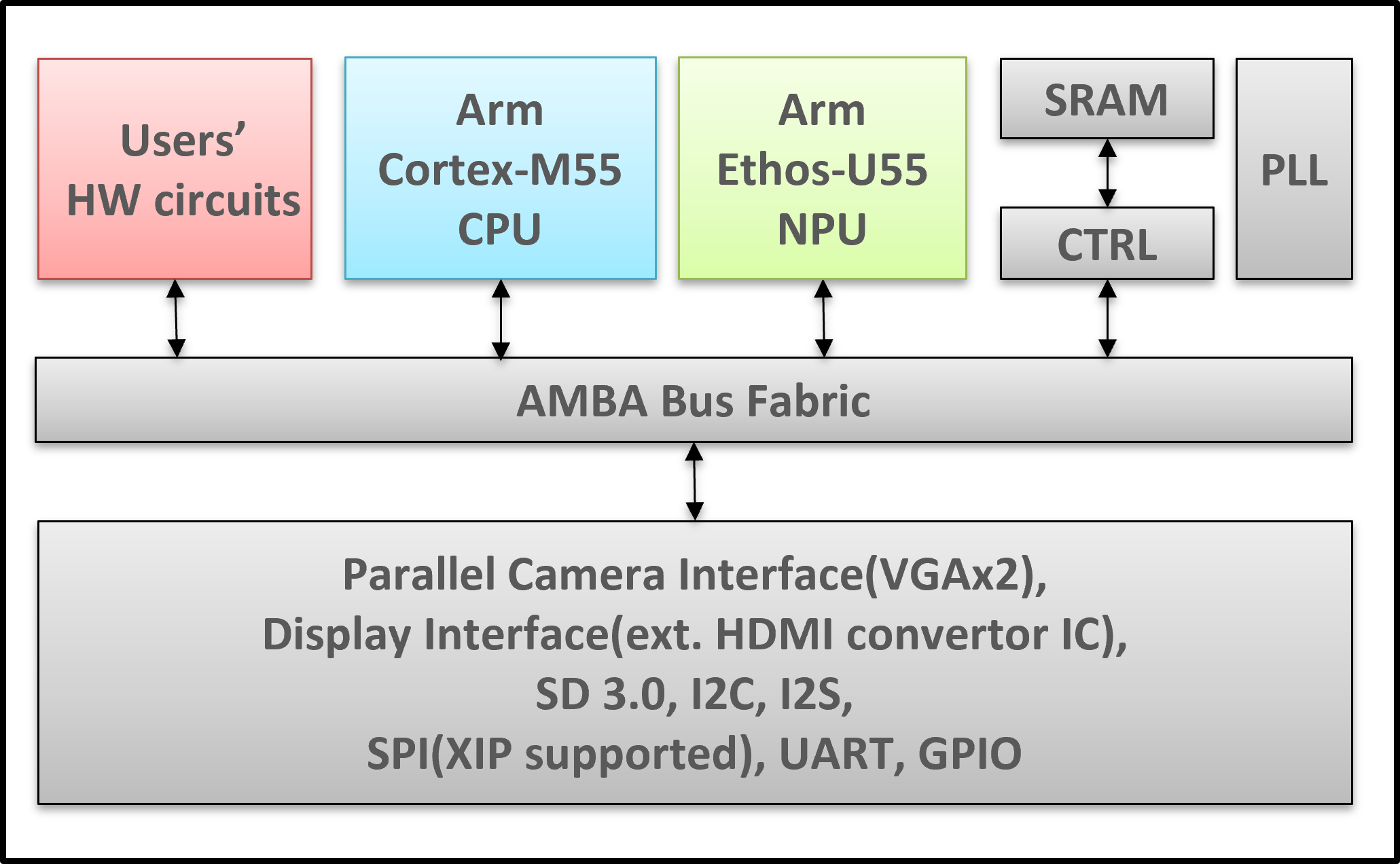

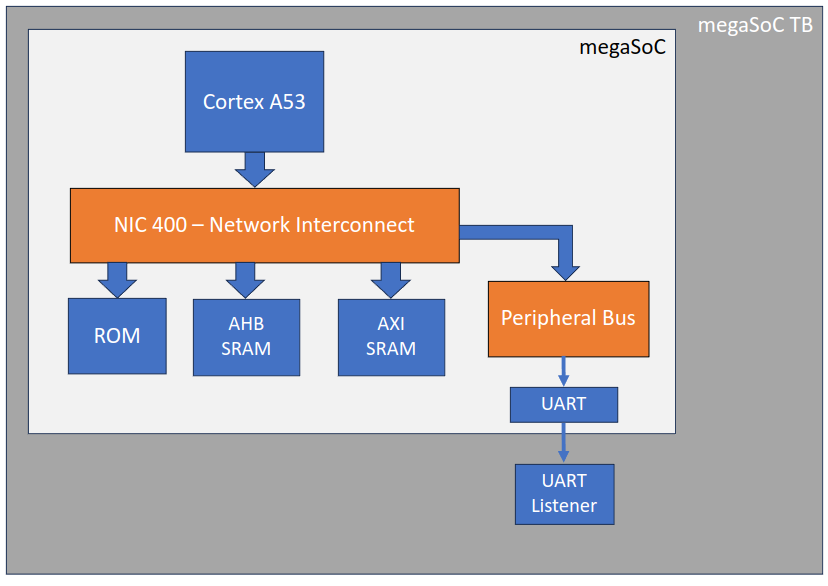

megasoc has been designed to provide a complex SoC component that can 'host' and support the development and evaluation of research components or subsystems. The design allows for seamless transition from FPGA to physical silicon implementation via a pre-verified programmable control system that allows reuse of software and diagnostic functionality to facilitate the configuration, control and diagnostic analysis of research hardware such as custom accelerators or signal processing.

Daniel Newbrook

Daniel Newbrook

David Flynn

David Flynn

Srimanth Tenneti

Srimanth Tenneti

John Darlington

John Darlington