All Projects

You can use the filters below to restrict this based on Technology or Skills.

The development of a Low-Cost and Low-Power Data Acquisition System(DAQs). The DAQs will be made up of end-terminal and a gateway. The end-terminal will be micro-controller-driven device built on a SoC FPGA technology with built-in capability for machine learning. The end-terminal will be able to transmit and receive data using the Low Power Wide Area Networking (LPWAN) communication protocol that functions on LoRA.LoRa is a wireless radio frequency technology that operates in a license-free radio frequency spectrum.

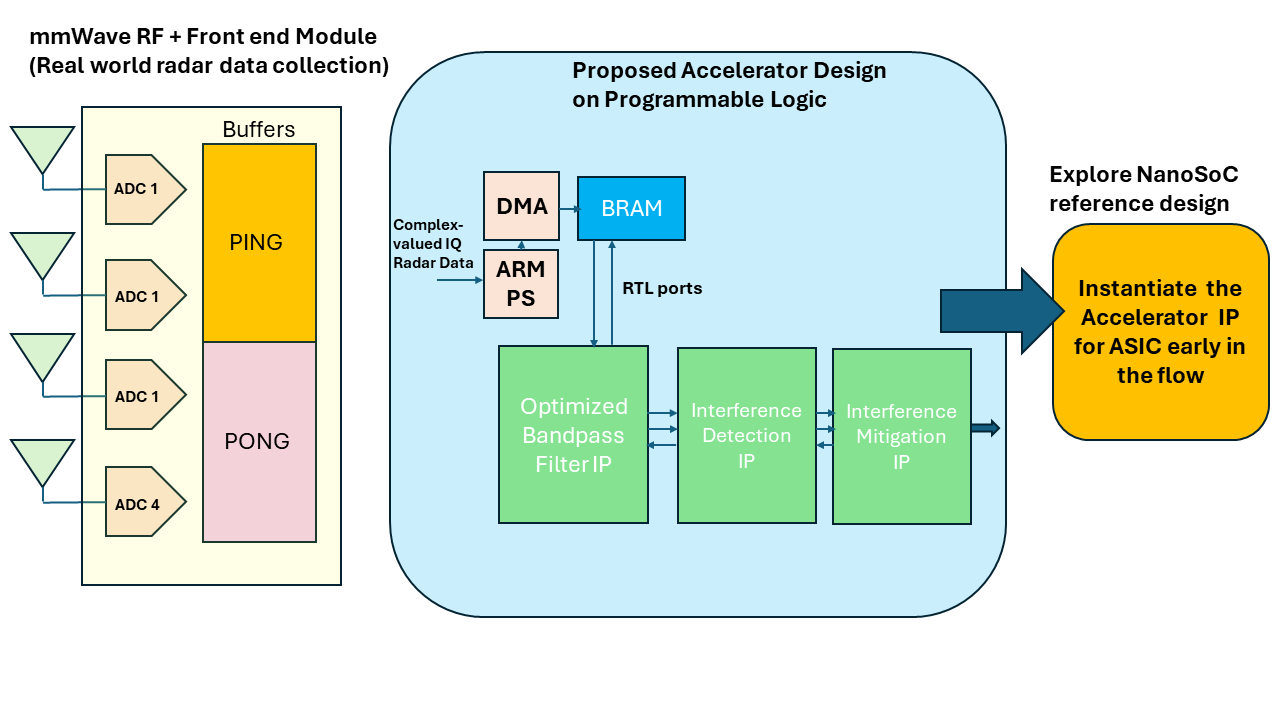

Advancements in electronics, wireless communications, and sensing technologies have made possible a multitude of smart sensing features in automotives. Integrating high-frequency sensors, digital signal processors and hardware accelerator engines on a single system on a chip (SoC) enhances sensing computation potential of radar sensors utilized in automotives.

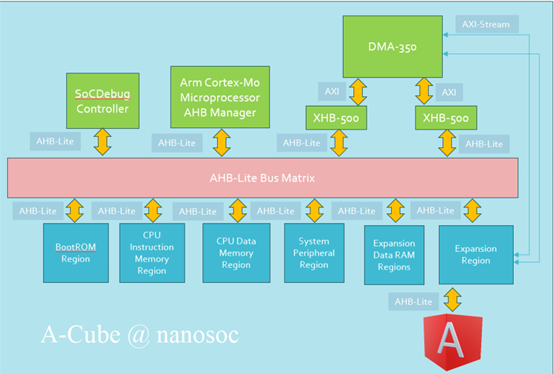

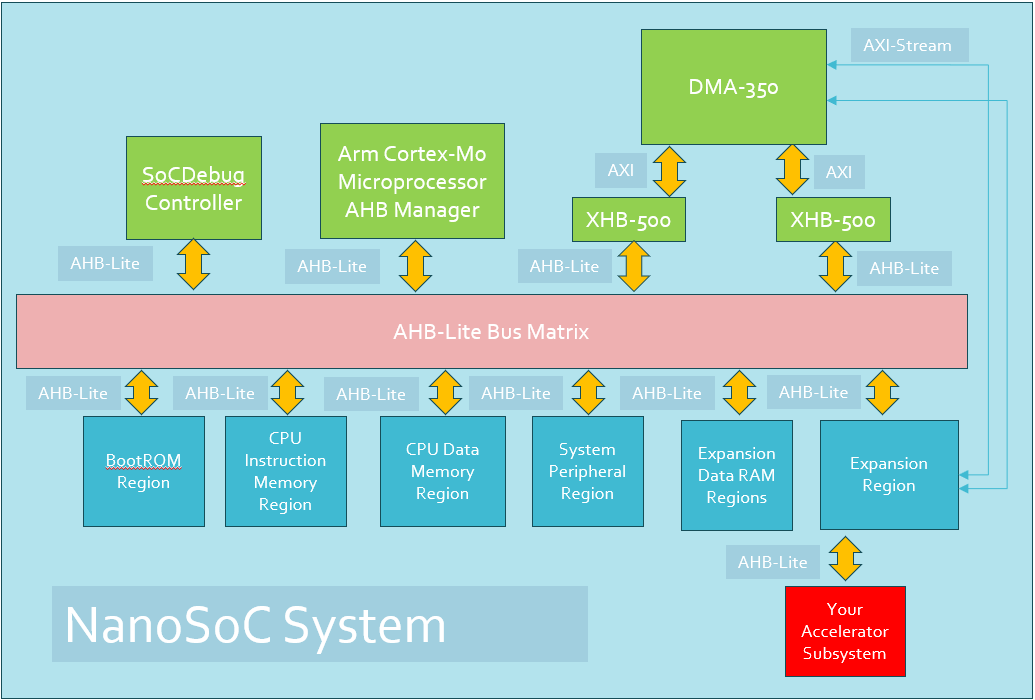

A physical test environment is required for ASIC devices fabricated following tape out. The nanoSoC test board provides a complete test environment for ASIC designs based on the nanoSoC reference design and enables the showcase of any custom designs that utilise it. Reviewing the function of nanoSoC identifies a number of design criteria for the test board:

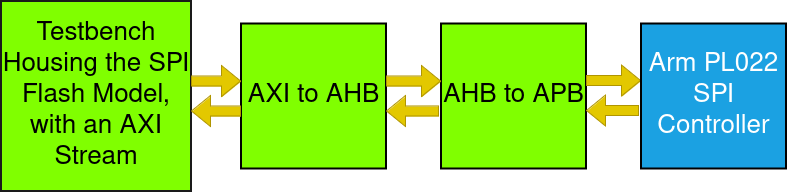

The Arm PL022 provides an interface for synchronous serial communication with peripheral devices connected to the SoC via the Advanced Peripheral Bus (APB). It supports a choice of interface operation, Motorola compatible Serial Peripheral Interface (SPI), National Semiconductor Microwire, or Texas Instruments synchronous serial interface. See the Techology page for details.

We propose the A-Cube design methodology to create medical decision support on the edge. The design and implementation of an atrial fibrillation detector hardware core was selected as a proof-of-concept study. To facilitate the required atrial fibrillation functionality, we adopted an established AI model, based on Long Short-Term Memory (LSTM) technology for hardware implementation. The adaptation was done by varying design parameters such as data window and the number of LSTM units.

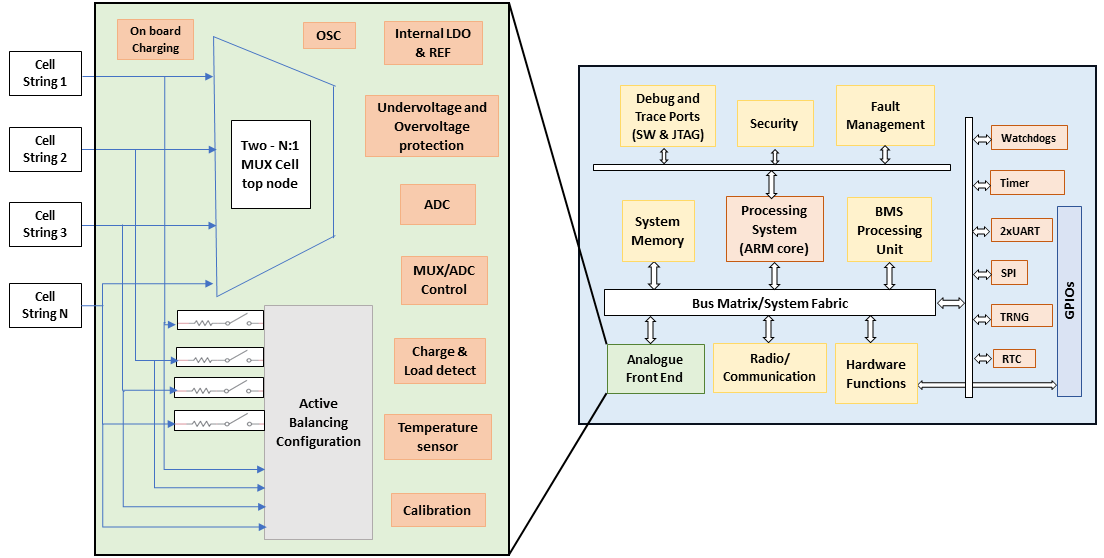

Battery storage systems are an important source for powering emerging clean energy applications. The Battery Management System (BMS) is a critical component of modern battery storage, essential for efficient system monitoring, reducing run-time failures, prolonging charge-discharge lifecycle, and preventing battery stress or catastrophic situations. The BMS performs functionalities such as data acquisition and monitoring, battery state estimation, cell equalization, and charge protection, making it computationally intensive to manage large scale battery storage.

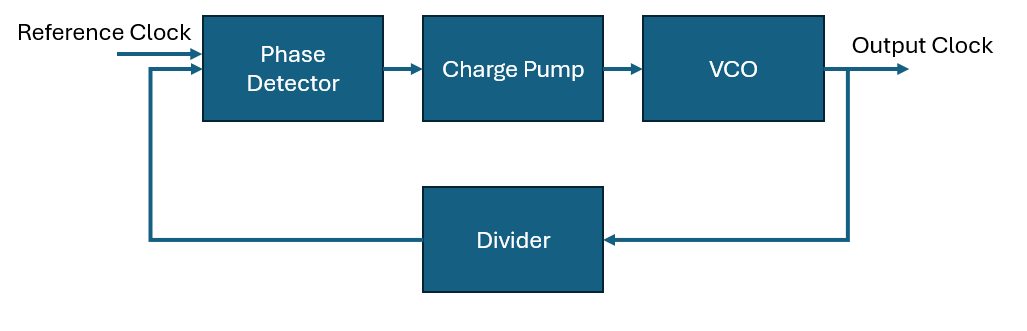

To design and verify a simple PLL for use as generator of clock signals in System on Chip design. The desired outcome from this project should be the following:

Clock generation for frequencies between 60 MHz and 1.2 GHzInclude PLL-lock signal for system start upLow clock uncertainty below 5% (transition time and jitter)Integer clock divider which can be updated at run timeMinimal areaThe resulting IP for these component blocks will be made available to the soclabs community for the upcoming design contest.

The dynamic range processor is a DSP function which does as it says on the tin; it compresses the dynamic range of the incoming signal. This is used most commonly in the music industry for its effects on the perceived loudness of audio. It is also used extensively in hearing aids to compensate for the user’s reduced dynamic range of hearing. In this project a hardware accelerator is developed for the purpose of dynamic range compression of digital audio. This accelerator will be implemented in a mixed-signal infrastructure.

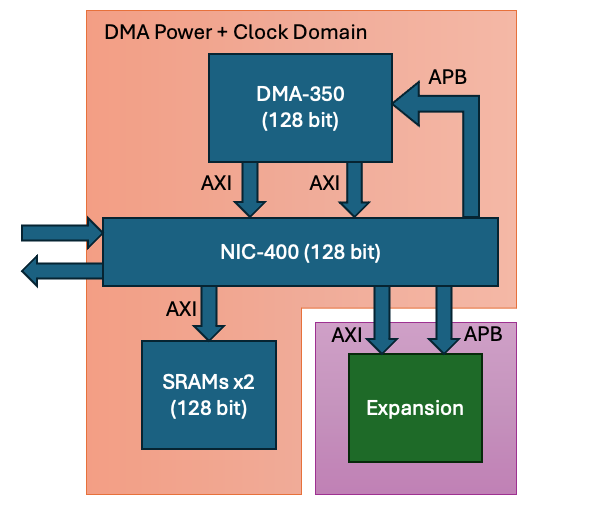

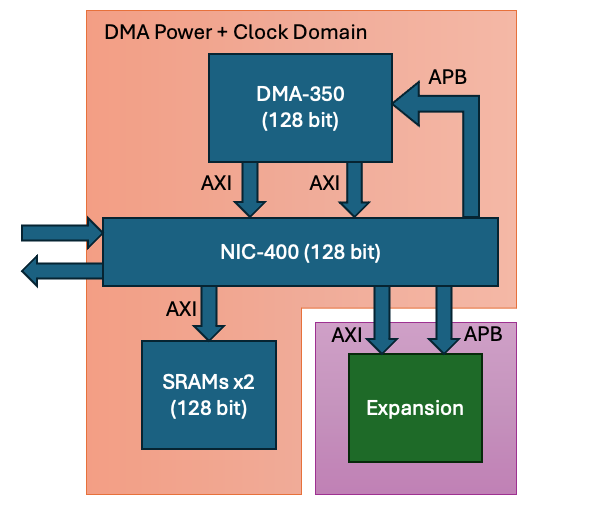

The integration of the DMA350 into the nanosoc re-usable SoC architecture improves the transfer bandwidth on DMA channels within the SoC. This project integrates the DMA 350 into nanosoc, validates the integration and functionality of the DMA 350, and compares the performance of the DMA 350 to the PL230, the first DMA controller integrated into nanosoc.

Daniel Newbrook

Daniel Newbrook

Ayodeji Oluwatope

Ayodeji Oluwatope

rami hariri

rami hariri

Rashi Dutt

Rashi Dutt

Peter Richards

Peter Richards