The Synopsys HAPS® System adds additional capabilities to the FPGA-based prototyping environments SoC Labs can use to support projects. The HAPS® system provides a greater amount of logic resources supporting the development of larger SoC designs. It can be used to support multiple projects simultaneously. It is used by many semiconductor companies, including ARM, for their CPU verification. This collaboration project will use the HAPS® system in SoC Labs projects and share with the community experience in utilising such systems.

All Projects

You can use the filters below to restrict this based on Technology or Skills.

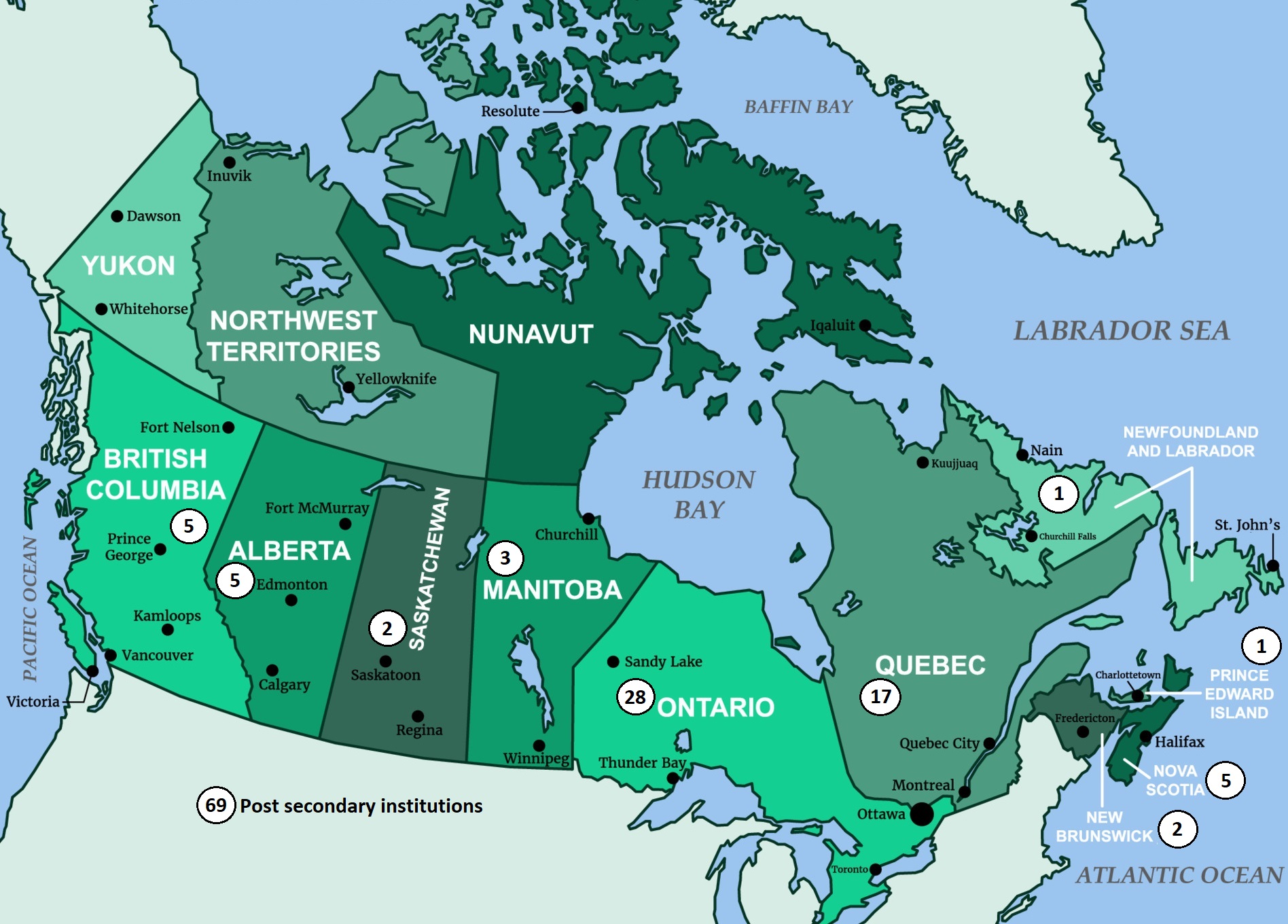

This collaboration project is aimed at providing specific tailored activities to the local geography in Canada by developing local actions that will help stimulate academics and their institutions and the broader semiconductor industry supporters to create new and exciting SoC design projects. It may include:

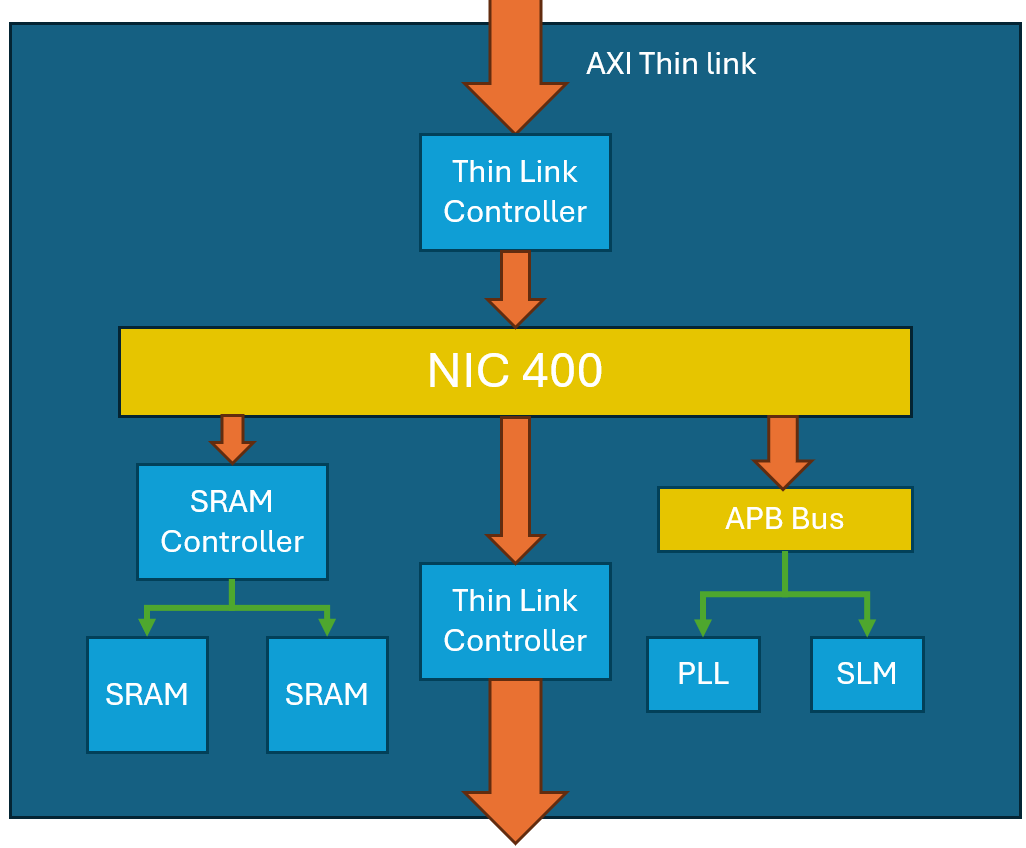

On-chip SRAM in ASICs can use a significant area, which equates to a significant cost. One solution is to make the memory off-chip. This project explores the use of Arm IP to create an SRAM chiplet design. The benefit is that standard memory chiplets can be fabricated at lower cost and used across multiple projects, miminising silicon area to the unique project needs.

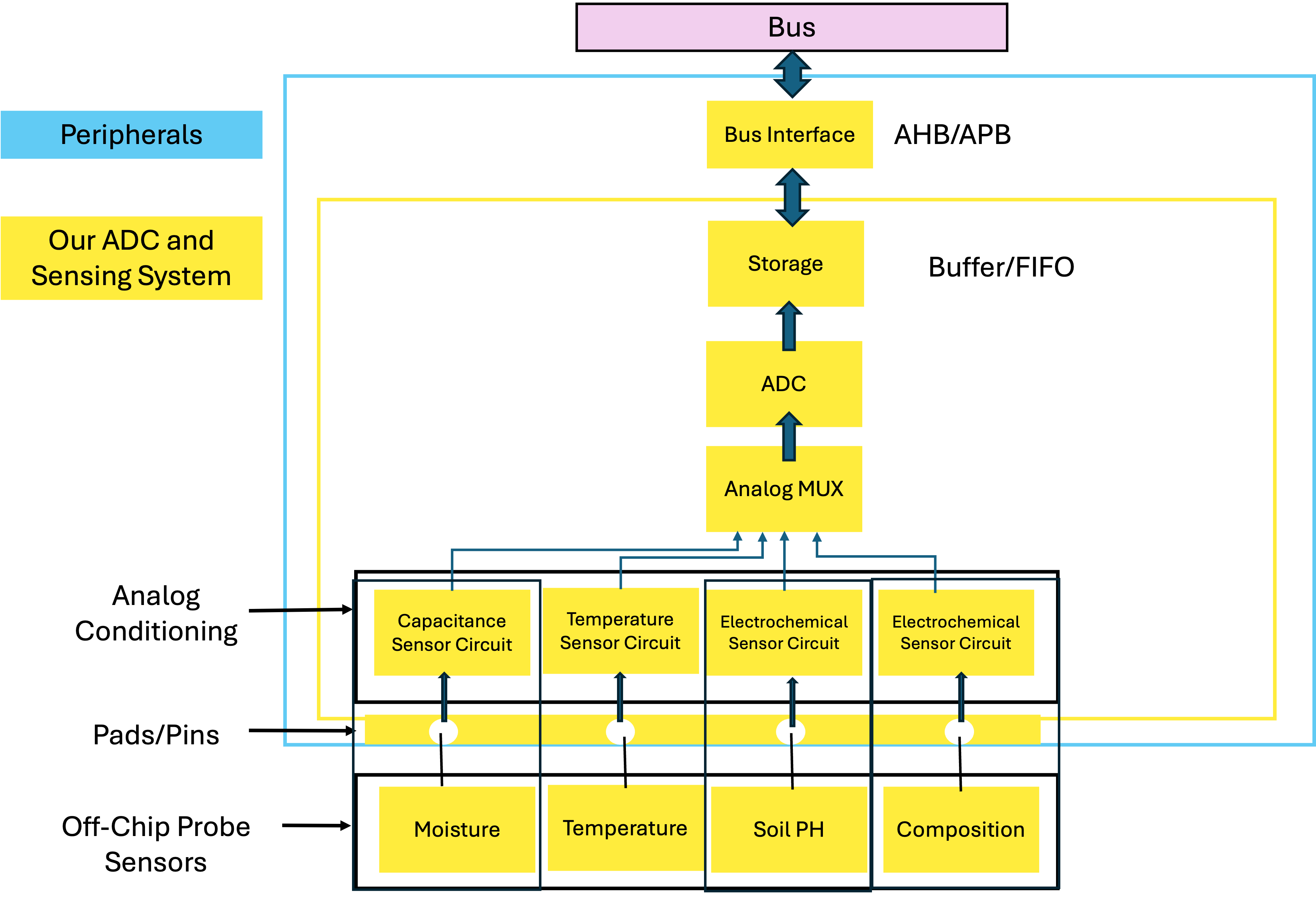

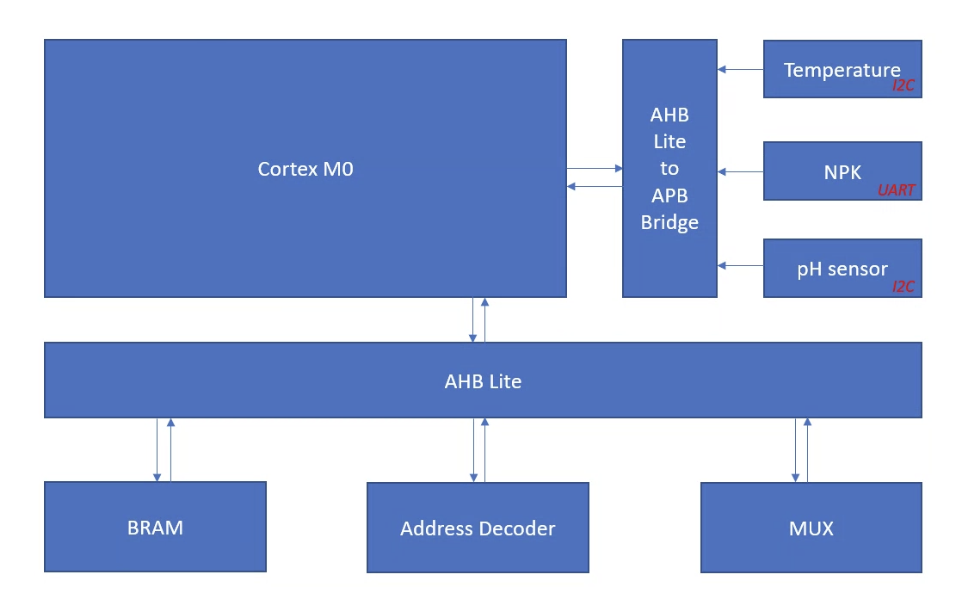

Our innovative SoC design for precision agriculture revolutionizes field management by deploying a robust mesh network of sensor-based devices, capable of detailed monitoring and swift response to variations in soil health, erosion, drought, and pest activities. This system not only ensures reliability through its mesh architecture—eliminating single points of failure—but also incorporates diverse sensors for comprehensive data acquisition. It's engineered for energy efficiency to sustain operation throughout an entire crop season, significantly optimizing resource use and reducing waste.

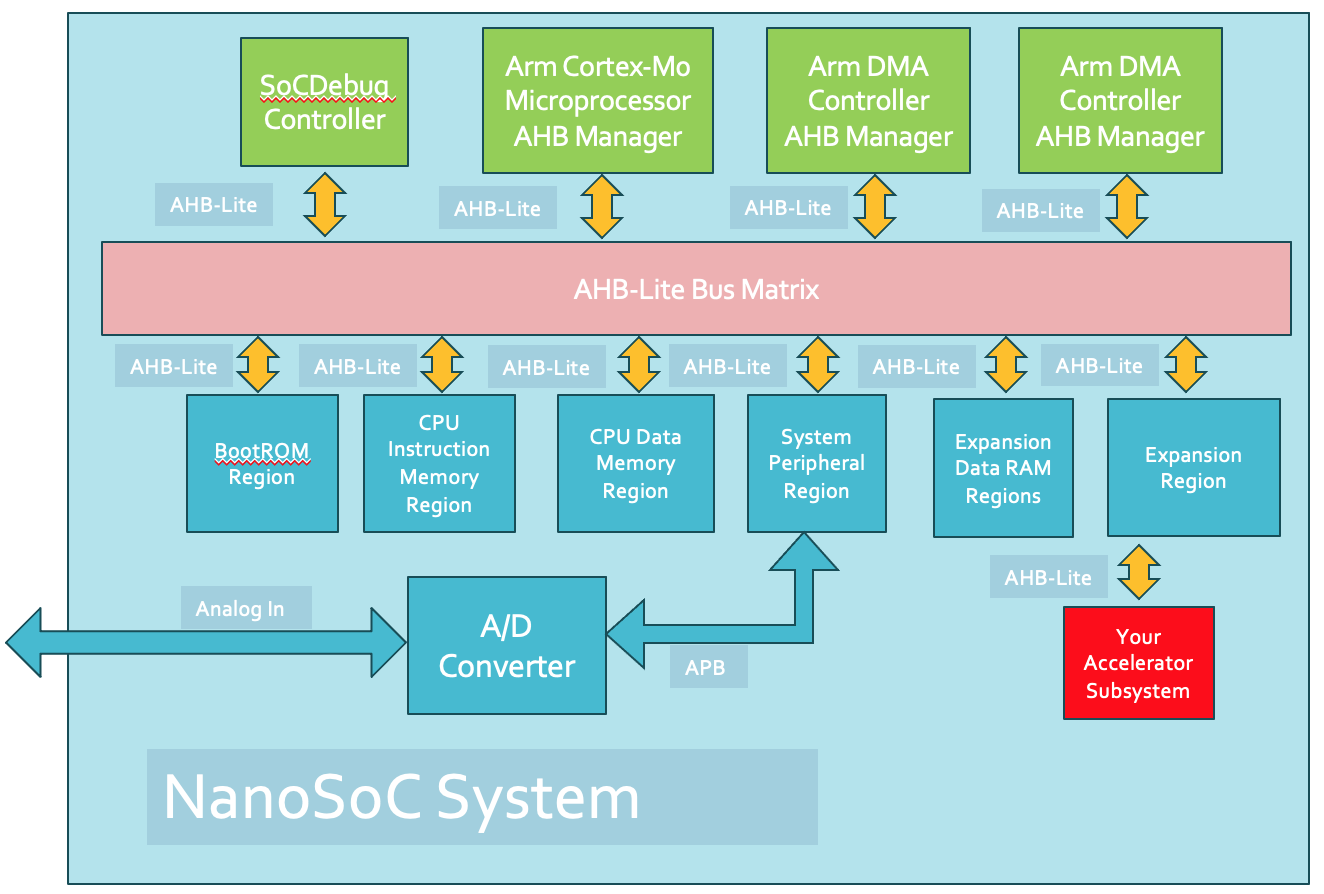

The aim of this project is to define a mixed signal subsystem for the nanosoc reference design.

The mixed signal subsystem should be able to sample analog signals at a regular sampling rate, and transmit a digital representation of this signal to the rest of the nanosoc system. In order to interface with real-world signals in a digital System on Chip ("SoC"), an analog to digital conversion ("ADC") is needed.

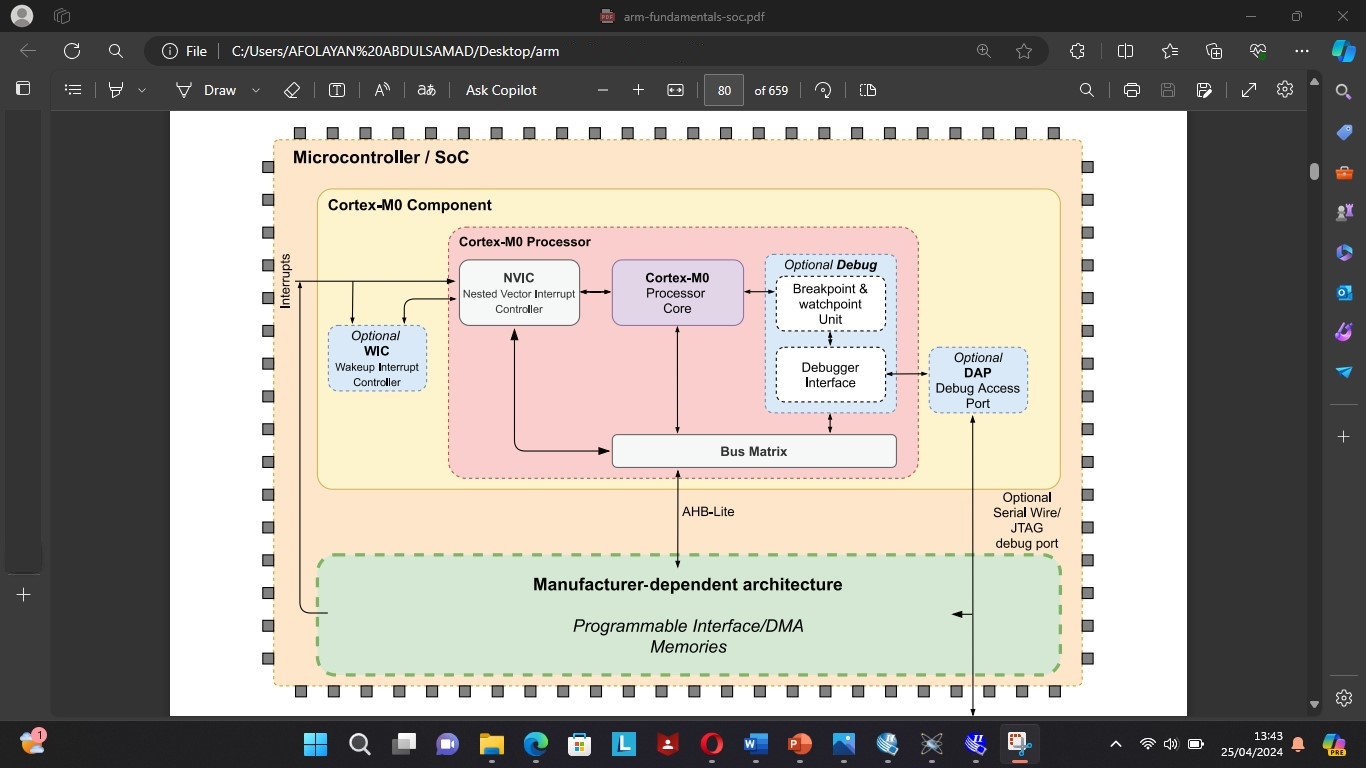

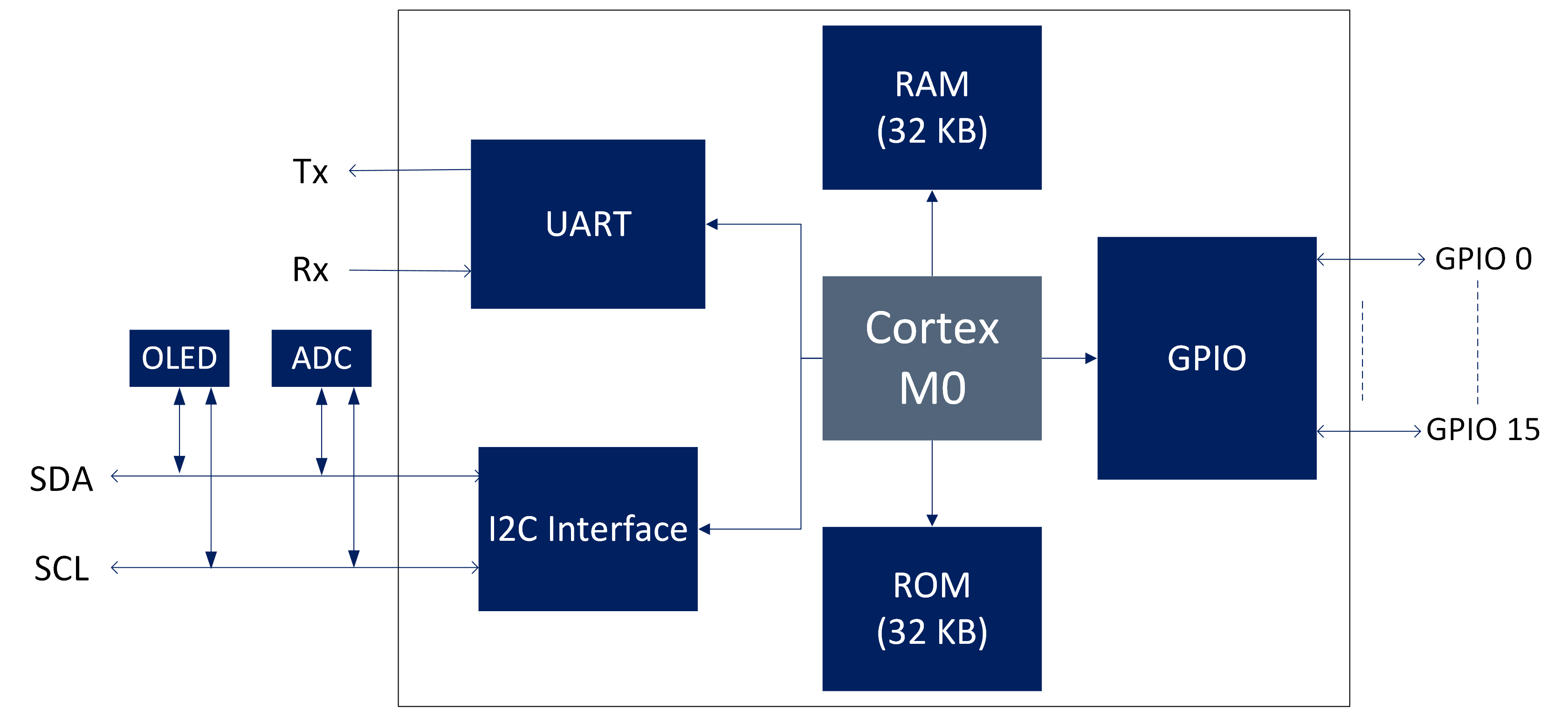

This project focuses on developing a plant growth monitoring system for space exploration missions using the ARM Cortex-M0 microcontroller core. The projects aim to develop a SOC based on ARM M0 core for interactive plant monitoring by interfacing AHB lite, GPIO, timers, and communication protocols such as UART, I2C, SPI, and co-processors. This project also proposes two co-processors for interactive plant monitoring and control. One AI co-processor for classification and prediction of plant and environmental data.

Nowadays, rotating machine is the power source for most production equipment and is widely used in manufacturing factories. Common rotating machinery mainly includes bearings, gears, shafts, and the others. However, rotating machines suffer from frequent collisions and vibrations which lead to wearing and aging, which increases the chance of failure in the overall system operation. This make the cost of factories increase and the quality of production deteriorate. Therefore, the industries gradually value the usage of accurate and efficiency predictive maintenance system.

This Project is to develop traffic light system that can reduce traffic congestion with the aid of counters for each lane and acts wisely with the intersection in real time based with a fixed time constrain, include both hardware and software requirements using SOC FPGA technology with fundamental specification for the Register Transfer Level (RTL).

Conventional healthcare is expensive and reliant on the physical presence of the patients. Continuous health monitoring tracks vital health parameters like heart rate, blood pressure, etc. While these work well in measuring the parameters, modern-day devices rely on the cloud to compute and interpret data. This results in an increase in data transfer between the device and the cloud, and if this connection breaks, there can be no interpretation of data. Hence, there is a need to shift the computation to the hardware, referred to as "Edge Computing".

John Darlington

John Darlington

Daniel Newbrook

Daniel Newbrook

AFOLAYAN, ABDULSAMAD

AFOLAYAN, ABDULSAMAD